# COMe-bTL6

User Guide. Rev. 2.4 Doc. ID: 1068 8679

This page has been intentionally left blank

# ► COME-BTL6 – USER GUIDE

#### Disclaimer

Kontron would like to point out that the information contained in this user guide may be subject to alteration, particularly as a result of the constant upgrading of Kontron products. This document does not entail any guarantee on the part of Kontron with respect to technical processes described in the user guide or any product characteristics set out in the user guide. Kontron assumes no responsibility or liability for the use of the described product(s), conveys no license or title under any patent, copyright or mask work rights to these products and makes no representations or warranties that these products are free from patent, copyright or mask work right infringement unless otherwise specified. Applications that are described in this user guide are for illustration purposes only. Kontron makes no representation or warranty that such application will be suitable for the specified use without further testing or modification. Kontron expressly informs the user that this user guide only contains a general description of processes and instructions which may not be applicable in every individual case. In cases of doubt, please contact Kontron.

This user guide is protected by copyright. All rights are reserved by Kontron. No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means (electronic, mechanical, photocopying, recording, or otherwise), without the express written permission of Kontron. Kontron points out that the information contained in this user guide is constantly being updated in line with the technical alterations and improvements made by Kontron to the products and thus this user guide only reflects the technical status of the products by Kontron at the time of publishing.

Brand and product names are trademarks or registered trademarks of their respective owners.

©2022 by Kontron Europe GmbH

Kontron Europe GmbH

Gutenbergstraße 2 85737 Ismaning Germany www.kontron.com

#### Intended Use

THIS DEVICE AND ASSOCIATED SOFTWARE ARE NOT DESIGNED, MANUFACTURED OR INTENDED FOR USE OR RESALE FOR THE OPERATION OF NUCLEAR FACILITIES, THE NAVIGATION, CONTROL OR COMMUNICATION SYSTEMS FOR AIRCRAFT OR OTHER TRANSPORTATION, AIR TRAFFIC CONTROL, LIFE SUPPORT OR LIFE SUSTAINING APPLICATIONS, WEAPONS SYSTEMS, OR ANY OTHER APPLICATION IN A HAZARDOUS ENVIRONMENT, OR REQUIRING FAIL-SAFE PERFORMANCE, OR IN WHICH THE FAILURE OF PRODUCTS COULD LEAD DIRECTLY TO DEATH, PERSONAL INJURY, OR SEVERE PHYSICAL OR ENVIRONMENTAL DAMAGE (COLLECTIVELY, "HIGH RISK APPLICATIONS").

You understand and agree that your use of Kontron devices as a component in High Risk Applications is entirely at your risk. To minimize the risks associated with your products and applications, you should provide adequate design and operating safeguards. You are solely responsible for compliance with all legal, regulatory, safety, and security related requirements concerning your products. You are responsible to ensure that your systems (and any Kontron hardware or software components incorporated in your systems) meet all applicable requirements. Unless otherwise stated in the product documentation, the Kontron device is not provided with error-tolerance capabilities and cannot therefore be deemed as being engineered, manufactured or setup to be compliant for implementation or for resale as device in High Risk Applications. All application and safety related information in this document (including application descriptions, suggested safety measures, suggested Kontron products, and other materials) is provided for reference only.

**ACAUTION**

Handling and operation of the product is permitted only for trained personnel within a work place that is access controlled. Follow the "General Safety Instructions" supplied with the product.

NOTICE

You find the most recent version of the "General Safety Instructions" online in the download area of this product.

NOTICE

This product is not suited for storage or operation in corrosive environments, in particular under exposure to sulfur and chlorine and their compounds. For information on how to harden electronics and mechanics against these stress conditions, contact Kontron Support.

# **Revision History**

| Revision | Brief Description of Changes                                                                                                                                                                | Date of Issue | Author |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------|

| 1.0      | Initial version                                                                                                                                                                             | 2022-Apr-08   | CW     |

| 1.1      | Ch. 2.3.3 Block Diagram and Ch. 2.3.12 PCIE Express Graphics (PEG) Gen 4 updated.                                                                                                           | 2022-May-03   | CW     |

| 1.2      | I2C pin numbering changed Ch 4.1 and added corrosive warning pg. 4.                                                                                                                         | 2022-May-19   | CW     |

| 1.3      | Typo "PCIe configuration (8x1)" in chapter 2.3.11 corrected.                                                                                                                                | 2022-May-24   | hjs    |

| 1.4      | Updated Table 4 Memory Accessories and Chapter 3.4 GPIO.                                                                                                                                    | 2022- July-19 | CW     |

| 1.5      | Update Ch. 5 COMe connector pin assignment tables.                                                                                                                                          | 2022-Aug-30   | CW     |

| 1.6      | Updated, Figure 1, HSIO signal names in Tables 11, 12, 14, and 16 and updated the following in pinout tables (PCIE_TX5+/-, PCIE_RX6+/-, PCIE_RX7+/-, PEG_LANE-Reversal and Rapid Shutdown.) | 2022-Nov-07   | CW     |

| 1.7      | Updated support of non ECC/ECC in Table 2.                                                                                                                                                  | 2022-Dec-12   | CW     |

| 1.8      | Update the cooling accessory information in Table 4                                                                                                                                         | 2022-Dec-22   | CW     |

| 1.9      | Updated description of Ethernet pins A4 and A5 and new logo                                                                                                                                 | 2023-Feb-15   | CW     |

| 2.0      | 2.4.1.2 Voltage ripple changed to 200 mV and added the new logo.                                                                                                                            | 2023-Aug-23   | CW     |

| 2.1      | PCIe GEN4 is supported on all available PEG Ports.                                                                                                                                          | 2023-Nov-20   | CW     |

| 2.2      | SPI boot flash device updated in Table 33.                                                                                                                                                  | 2024-Jan-10   | CW     |

| 2.3      | Chapter 2.3.5 DTR update and new Kontron Logo                                                                                                                                               | 2024-05-23    | CW     |

| 2.4      | Updated Table 17 Eeep 32 Kbytes changes to 1 Kbyte                                                                                                                                          | 2025-01-27    | CW     |

### **Terms and Conditions**

Kontron warrants products in accordance with defined regional warranty periods. For more information about warranty compliance and conformity, and the warranty period in your region, visit <a href="http://www.kontron.com/terms-and-conditions">http://www.kontron.com/terms-and-conditions</a>.

Kontron sells products worldwide and declares regional General Terms & Conditions of Sale, and Purchase Order Terms & Conditions. Visit <a href="http://www.kontron.com/terms-and-conditions">http://www.kontron.com/terms-and-conditions</a>.

For contact information, refer to the corporate offices contact information on the last page of this user guide or visit our website <u>CONTACT US</u>.

# **Customer Support**

Find Kontron contacts by visiting Kontron Support: <a href="https://www.kontron.com/en/support-and-services">https://www.kontron.com/en/support-and-services</a>.

### **Customer Service**

As a trusted technology innovator and global solutions provider, Kontron extends its embedded market strengths into a services portfolio allowing companies to break the barriers of traditional product lifecycles. Proven product expertise coupled with collaborative and highly-experienced support enables Kontron to provide exceptional peace of mind to build and maintain successful products.

For more details on Kontron's service offerings such as: enhanced repair services, extended warranty, Kontron training academy, and more visit <a href="https://www.kontron.com/en/support-and-services">https://www.kontron.com/en/support-and-services</a>.

# **Customer Comments**

If you have any difficulties using this user guide, discover an error, or just want to provide some feedback, contact Kontron Support. Detail any errors you find. We will correct the errors or problems as soon as possible and post the revised user guide on our website.

# **Symbols**

The following symbols may be used in this user guide

#### **ADANGER**

DANGER indicates a hazardous situation which, if not avoided, will result in death or serious injury.

#### **AWARNING**

WARNING indicates a hazardous situation which, if not avoided, could result in death or serious injury.

### NOTICE

NOTICE indicates a property damage message.

#### **A**CAUTION

CAUTION indicates a hazardous situation which, if not avoided, may result in minor or moderate injury.

#### Electric Shock!

This symbol and title warn of hazards due to electrical shocks (> 60 V) when touching products or parts of products. Failure to observe the precautions indicated and/or prescribed by the law may endanger your life/health and/or result in damage to your material.

#### **ESD Sensitive Device!**

This symbol and title inform that the electronic boards and their components are sensitive to static electricity. Care must therefore be taken during all handling operations and inspections of this product in order to ensure product integrity at all times.

#### **HOT Surface!**

Do NOT touch! Allow to cool before servicing.

#### Laser!

This symbol informs of the risk of exposure to laser beam and light emitting devices (LEDs) from an electrical device. Eye protection per manufacturer notice shall review before servicing.

This symbol indicates general information about the product and the user guide.

This symbol also indicates detail information about the specific product configuration.

This symbol precedes helpful hints and tips for daily use.

# For Your Safety

Your new Kontron product was developed and tested carefully to provide all features necessary to ensure its compliance with electrical safety requirements. It was also designed for a long fault-free life. However, the life expectancy of your product can be drastically reduced by improper treatment during unpacking and installation. Therefore, in the interest of your own safety and of the correct operation of your new Kontron product, you are requested to conform with the following guidelines.

#### **High Voltage Safety Instructions**

As a precaution and in case of danger, the power connector must be easily accessible. The power connector is the product's main disconnect device.

#### **ACAUTION**

#### Warning

All operations on this product must be carried out by sufficiently skilled personnel only.

#### **A**CAUTION

#### Electric Shock!

Before installing a non hot-swappable Kontron product into a system always ensure that your mains power is switched off. This also applies to the installation of piggybacks. Serious electrical shock hazards can exist during all installation, repair, and maintenance operations on this product. Therefore, always unplug the power cable and any other cables which provide external voltages before performing any work on this product.

Earth ground connection to vehicle's chassis or a central grounding point shall remain connected. The earth ground cable shall be the last cable to be disconnected or the first cable to be connected when performing installation or removal procedures on this product.

### Special Handling and Unpacking Instruction

#### NOTICE

#### **ESD Sensitive Device!**

Electronic boards and their components are sensitive to static electricity. Therefore, care must be taken during all handling operations and inspections of this product, in order to ensure product integrity at all times.

Do not handle this product out of its protective enclosure while it is not used for operational purposes unless it is otherwise protected.

Whenever possible, unpack or pack this product only at EOS/ESD safe work stations. Where a safe work station is not guaranteed, it is important for the user to be electrically discharged before touching the product with his/her hands or tools. This is most easily done by touching a metal part of your system housing.

It is particularly important to observe standard anti-static precautions when changing piggybacks, ROM devices, jumper settings etc. If the product contains batteries for RTC or memory backup, ensure that the product is not placed on conductive surfaces, including anti-static plastics or sponges. They can cause short circuits and damage the batteries or conductive circuits on the product.

# **Lithium Battery Precautions**

If your product is equipped with a lithium battery, take the following precautions when replacing the battery.

#### Danger of explosion if the battery is replaced incorrectly.

- Replace only with same or equivalent battery type recommended by the manufacturer.

- Dispose of used batteries according to the manufacturer's instructions.

# General Instructions on Usage

In order to maintain Kontron's product warranty, this product must not be altered or modified in any way. Changes or modifications to the product, that are not explicitly approved by Kontron and described in this user guide or received from Kontron Support as a special handling instruction, will void your warranty.

This product should only be installed in or connected to systems that fulfill all necessary technical and specific environmental requirements. This also applies to the operational temperature range of the specific board version that must not be exceeded. If batteries are present, their temperature restrictions must be taken into account.

In performing all necessary installation and application operations, only follow the instructions supplied by the present user guide.

Keep all the original packaging material for future storage or warranty shipments. If it is necessary to store or ship the product, then re-pack it in the same manner as it was delivered.

Special care is necessary when handling or unpacking the product. See Special Handling and Unpacking Instruction.

# Quality and Environmental Management

Kontron aims to deliver reliable high-end products designed and built for quality, and aims to complying with environmental laws, regulations, and other environmentally oriented requirements. For more information regarding Kontron's quality and environmental responsibilities, visit <a href="http://www.kontron.com/about-kontron/corporate-responsibility/quality-management">http://www.kontron.com/about-kontron/corporate-responsibility/quality-management</a>.

### Disposal and Recycling

Kontron's products are manufactured to satisfy environmental protection requirements where possible. Many of the components used are capable of being recycled. Final disposal of this product after its service life must be accomplished in accordance with applicable country, state, or local laws or regulations.

### **WEEE Compliance**

The Waste Electrical and Electronic Equipment (WEEE) Directive aims to:

- Reduce waste arising from electrical and electronic equipment (EEE)

- Make producers of EEE responsible for the environmental impact of their products, especially when the product become waste

- Encourage separate collection and subsequent treatment, reuse, recovery, recycling and sound environmental disposal of EEE

- Improve the environmental performance of all those involved during the lifecycle of EEE

Environmental protection is a high priority with Kontron.

Kontron follows the WEEE directive

You are encouraged to return our products for proper disposal.

# **Table of Contents**

| Symbols                                                          | 7  |

|------------------------------------------------------------------|----|

| For Your Safety                                                  | 8  |

| High Voltage Safety Instructions                                 | 8  |

| Special Handling and Unpacking Instruction                       | 8  |

| Lithium Battery Precautions                                      | 9  |

| General Instructions on Usage                                    | 9  |

| Quality and Environmental Management                             | 9  |

| Disposal and Recycling                                           | 9  |

| WEEE Compliance                                                  | 9  |

| Table of Contents                                                | 10 |

| List of Tables                                                   | 12 |

| List of Figures                                                  | 13 |

| 1/ Introduction                                                  |    |

| 1.1. Product Description                                         | 14 |

| 1.2. Product Naming Clarification                                |    |

| 1.3. COM Express® Documentation                                  |    |

| 1.4. COM Express® Functionality                                  |    |

| 1.5. COM Express® Benefits                                       |    |

| 2/ Product Specification                                         |    |

| 2.1. Module Variants                                             |    |

| 2.1.1. Commercial Grade Modules (0°C to +60°C)                   | 16 |

| 2.1.2. Extended temperature Grade Modules (E1, -25°C to 75°C)    |    |

| 2.1.3. Industrial Temperature Grade Modules (E2, -40°C to +85°C) |    |

| 2.2. Accessories                                                 |    |

| 2.3. Functional Specification                                    | 19 |

| 2.3.1. Technical Data                                            |    |

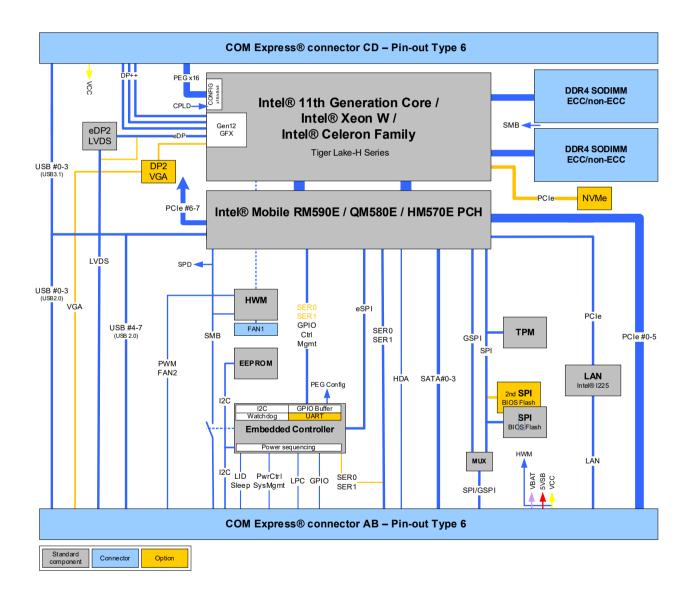

| 2.3.2. Block Diagram                                             |    |

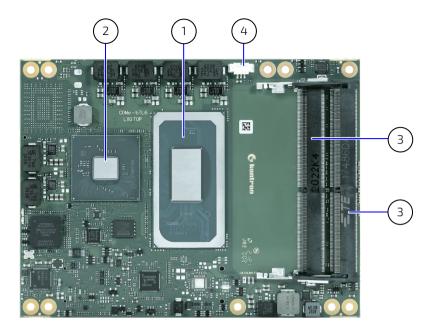

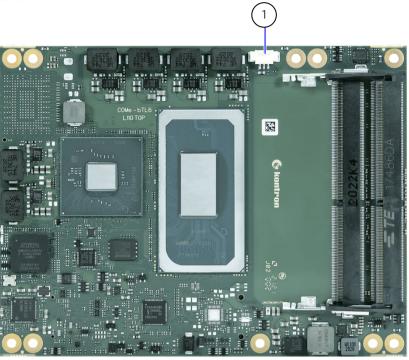

| 2.3.3. Front Side                                                |    |

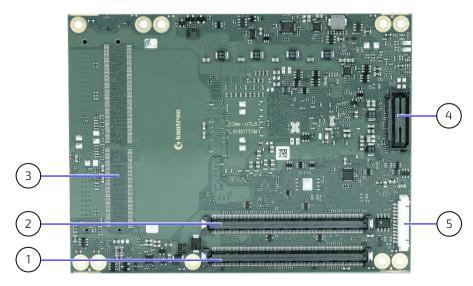

| 2.3.4. Rear Side                                                 |    |

| 2.3.5. Processor (CPU)                                           |    |

| 2.3.6. Chipset (PCH)                                             |    |

| 2.3.7. System Memory                                             | 23 |

| 2.3.8. Graphics Interfaces                                       | 24 |

| 2.3.9. HD Audio                                                  |    |

| 2.3.10. USB 3.1 Gen 2/USB 2.0                                    |    |

| 2.3.11. General Purpose PCI Express 3.0                          |    |

| 2.3.12. PCI Express Graphics (PEG) Gen4                          |    |

| 2.3.13. SATA 3.0                                                 |    |

| 2.3.14. Ethernet LAN                                             |    |

| 2.3.15. COMe High-speed Interface Overview                       |    |

| 2.3.16. Storage                                                  |    |

| 2.3.17. BIOS/Software Features                                   |    |

| 2.3.18. Additional Features                                      |    |

| 2.4. Electrical Specification                                    |    |

| 2.4.1. Power Supply Specification                                |    |

| 2.4.2. Power Management                                          |    |

| 2.4.2.2. Power Supply Control                                    | 32 |

| 2.4.3. Power Supply Modes                                                | 33 |

|--------------------------------------------------------------------------|----|

| 2.5. Thermal Management                                                  | 35 |

| 2.5.1. Heatspreader Plate Assembly                                       | 35 |

| 2.5.2. Active/Passive Cooling Solutions                                  | 35 |

| 2.5.3. Operating with Kontron Heatspreader Plate (HSP) Assembly          | 35 |

| 2.5.4. Operating without Kontron Heatspreader Plate (HSP) Assembly       | 35 |

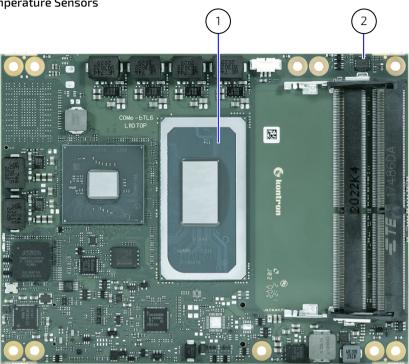

| 2.5.5. Temperature Sensors                                               | 36 |

| 2.5.6. On-Module Fan Connector                                           | 37 |

| 2.6. Environmental Specification                                         | 38 |

| 2.7. Compliance                                                          | 39 |

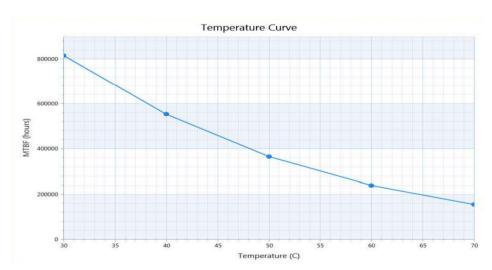

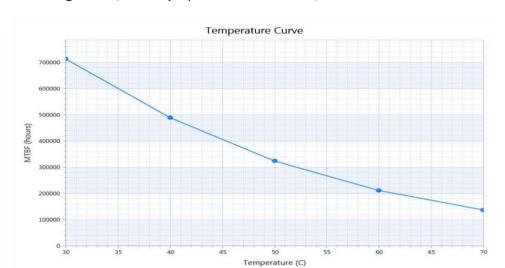

| 2.7.1. MTBF                                                              | 40 |

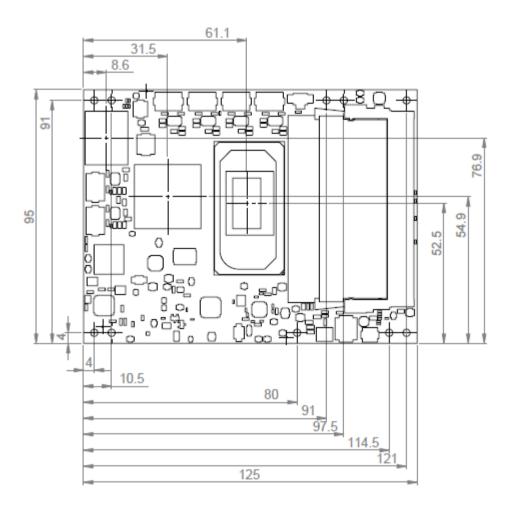

| 2.8. Mechanical Specification                                            |    |

| 2.8.1. Module Dimensions                                                 |    |

| 2.8.2. Module Height                                                     |    |

| 2.8.3. Heatspreader Plate Assembly Dimensions                            |    |

| 3/ Features and Interfaces                                               |    |

| 3.1. ACPI Power States                                                   |    |

| 3.2. eSPI (option)                                                       |    |

| 3.3. Fast I2C                                                            |    |

| 3.4. GPIO                                                                |    |

| 3.5. Hardware Monitor (HWM)                                              |    |

| 3.6. Intel® Optane™ (option)                                             |    |

| 3.7. LPC                                                                 |    |

| 3.8. NVMe Storage (Option)                                               |    |

| 3.9. SMB                                                                 |    |

| 3.10. Real Time Clock (RTC)                                              |    |

| 3.11. Serial Peripheral Interface (SPI)                                  |    |

| 3.11.1. Booting the SPI Flash Chip                                       |    |

| 3.11.2. SPI Boot                                                         |    |

| 3.11.3. External SPI Flash Boot on Modules with Intel® Management Engine |    |

| 3.12. TCC (Time Coordinated Computing)                                   |    |

| 3.13. TPM 2.0                                                            |    |

| 3.14. TSN (option)                                                       | 48 |

| 3.15. UART                                                               |    |

| 3.16. Watchdog Timer (WTD) Dual Stage                                    |    |

| 3.16.1. Watchdog Timer Signal                                            |    |

| 3.17. XDP (option)                                                       |    |

| 4/ System Resources                                                      |    |

| 4.1. I2C Bus                                                             |    |

| 4.2. System Management (SM) Bus                                          |    |

| 5/ COMe Interface Connector                                              |    |

| 5.1. Connecting COMe Interface Connector to Carrier Board                |    |

| 5.2. X1A and X1B Signals                                                 |    |

| 5.3. Connector (X1A) Row A1 – A110                                       |    |

| 5.4. Connector (X1A) Row B1 - B110                                       |    |

| 5.5. Connector (XIB) Row C1 - C110                                       |    |

| 5.6. Connector (X1B) Row D1 - D110                                       |    |

| 6/ UEFI BIOS                                                             |    |

| 6.1. Starting the uEFI BIOS                                              |    |

| U. 1. JUGI ULIŞ ULE ULLI LÜNDÜ                                           |    |

| 6.2. Navigating the uEFI BIOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 69                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 6.3. Getting Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 70                         |

| 6.4. Setup Menus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7C                         |

| 6.4.1. Main Setup Menu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 71                         |

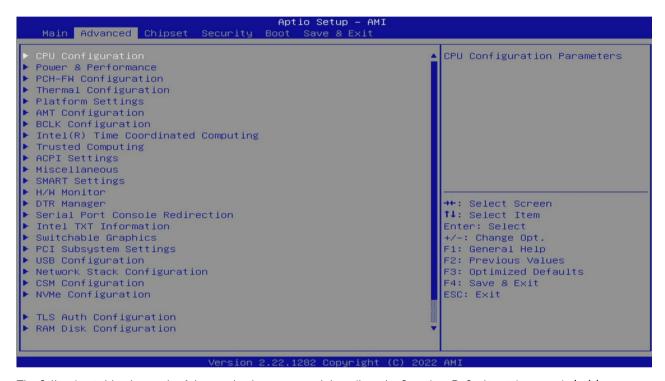

| 6.4.2. Advanced Setup Menu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 73                         |

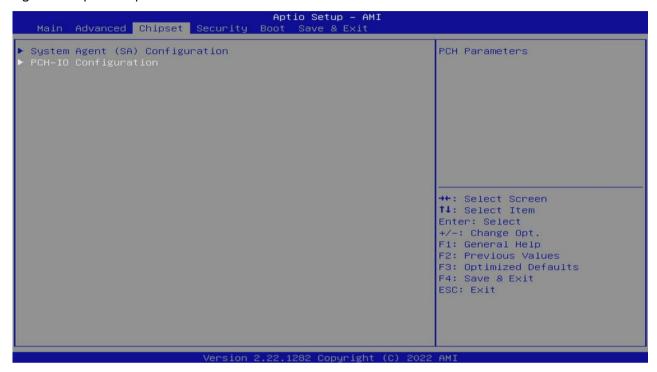

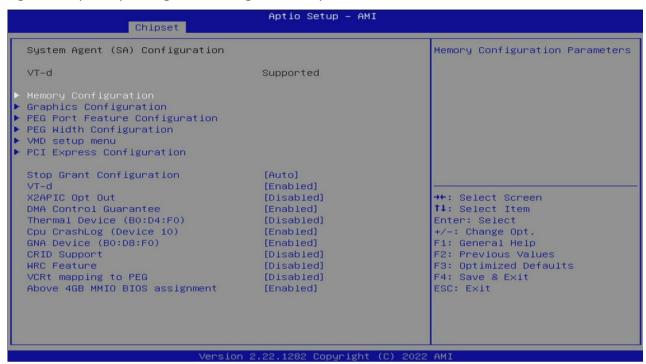

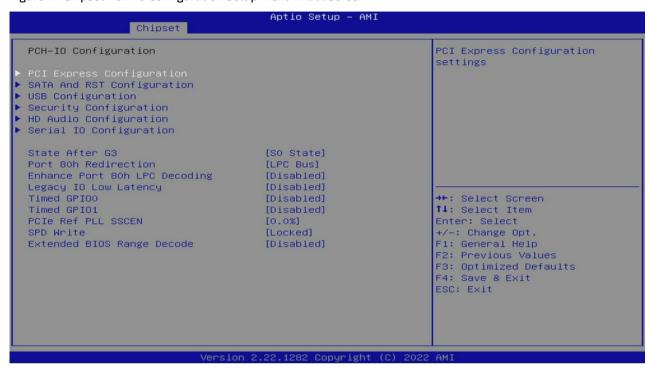

| 6.4.3. Chipset Setup Menu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |

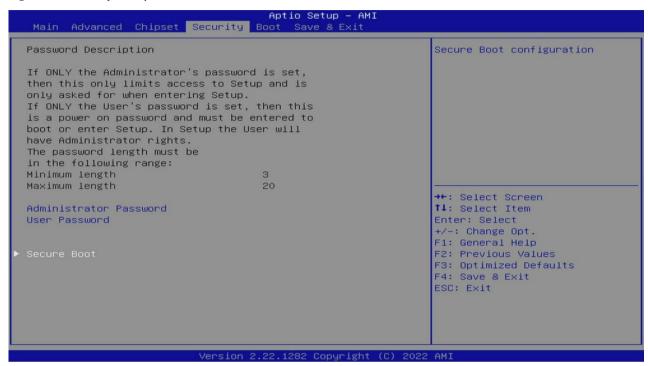

| 6.4.4. Security Setup Menu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            |

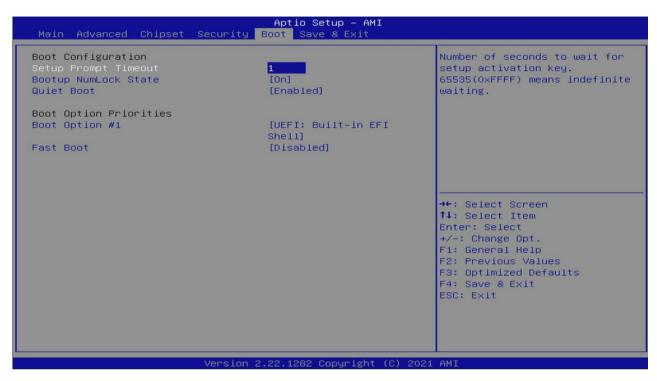

| 6.4.5. Boot Setup Menu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                            |

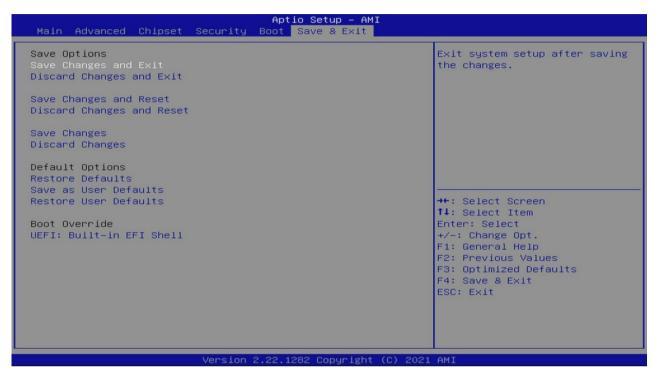

| 6.4.6. Save and Exit Setup Menu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |

| 6.5. uEFI Shell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            |

| 6.5.1. Entering the uEFI Shell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            |

| 6.5.2. Exiting the uEFI Shell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |

| 6.6. uEFI Shell Scripting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |

| 6.6.1. Startup Scripting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 100                        |

| 6.6.2. Create a Startup Script                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 100                        |

| 6.6.3. Example of Startup Scripts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 100                        |

| 6.7. Firmware Update                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 100                        |

| 7/ Technical Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 101                        |

| 7.1. Warranty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |

| 7.2. Returning Defective Merchandise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                            |

| List of Acronyms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                            |

| About Kontron                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |

| LISCOLIADIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |

| List of Tables  Table 1: Type 6 and COM-bTL6 Functionality  Table 2: Product Number for Commercial Grade Modules (0°C to +60°C operating)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16                         |

| Table 1: Type 6 and COM-bTL6 Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 16<br>17                   |

| Table 1: Type 6 and COM-bTL6 Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 16<br>17<br>17<br>17<br>19 |

| Table 1: Type 6 and COM-bTL6 Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 16<br>17<br>17<br>19       |

| Table 1: Type 6 and COM-bTL6 Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 16171922                   |

| Table 1: Type 6 and COM-bTL6 Functionality  Table 2: Product Number for Commercial Grade Modules (0°C to +60°C operating)  Table 3: Product Number for Industrial Grade Modules (-40°C to +85°C operating)  Table 4: Accessories  Table 5: Technical Data  Table 6: 11 <sup>th</sup> Generation Intel® Core™ Celeron® and Xeon® W Processor Spec  Table 7: Chipset (PCH)  Table 8: System Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                            |

| Table 1: Type 6 and COM-bTL6 Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            |

| Table 1: Type 6 and COM-bTL6 Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            |

| Table 1: Type 6 and COM-bTL6 Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            |

| Table 1: Type 6 and COM-bTL6 Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            |

| Table 1: Type 6 and COM-bTL6 Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            |

| Table 1: Type 6 and COM-bTL6 Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            |

| Table 1: Type 6 and COM-bTL6 Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            |

| Table 1: Type 6 and COM-bTL6 Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            |

| Table 1: Type 6 and COM-bTL6 Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            |

| Table 1: Type 6 and COM-bTL6 Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            |

| Table 1: Type 6 and COM-bTL6 Functionality  Table 2: Product Number for Commercial Grade Modules (0°C to +60°C operating)  Table 3: Product Number for Industrial Grade Modules (-40°C to +85°C operating)  Table 4: Accessories  Table 5: Technical Data  Table 6: 11 <sup>th</sup> Generation Intel® Core™ Celeron® and Xeon® W Processor Spec  Table 7: Chipset (PCH)  Table 8: System Memory  Table 9: Display Resolution  Table 10: Supported Display Types  Table 11: USB 3.1 Gen 2/USB 2.0 Port Configuration  Table 12: General Purpose PCI Express 3.0 Lane Configurations  Table 13: PCI Express Graphics (PEG) Lane Configurations  Table 14: SATA Port Connections  Table 15: Ethernet Port Connections  Table 16: High-speed IO (HSIO) Lane Combinations  Table 17: Storage features:  Table 18: BIOS and Software Features  Table 19: General, Special Kontron and Optional Features  Table 20: Electrical Specification                                                                       |                            |

| Table 1: Type 6 and COM-bTL6 Functionality  Table 2: Product Number for Commercial Grade Modules (0°C to +60°C operating)  Table 3: Product Number for Industrial Grade Modules (-40°C to +85°C operating)  Table 4: Accessories  Table 5: Technical Data  Table 6: 11th Generation Intel® Core™ Celeron® and Xeon® W Processor Spec  Table 7: Chipset (PCH)  Table 8: System Memory  Table 9: Display Resolution  Table 10: Supported Display Types  Table 11: USB 3.1 Gen 2/USB 2.0 Port Configuration  Table 12: General Purpose PCI Express 3.0 Lane Configurations  Table 13: PCI Express Graphics (PEG) Lane Configurations  Table 14: SATA Port Connections  Table 15: Ethernet Port Connections  Table 16: High-speed IO (HSIO) Lane Combinations  Table 17: Storage features:  Table 18: BIOS and Software Features  Table 19: General, Special Kontron and Optional Features  Table 20: Electrical Specification  Table 21: Power Supply Control Settings                                          |                            |

| Table 1: Type 6 and COM-bTL6 Functionality  Table 2: Product Number for Commercial Grade Modules (0°C to +60°C operating).  Table 3: Product Number for Industrial Grade Modules (-40°C to +85°C operating).  Table 4: Accessories  Table 5: Technical Data  Table 6: 11th Generation Intel® Core™ Celeron® and Xeon® W Processor Spec  Table 7: Chipset (PCH)  Table 8: System Memory  Table 9: Display Resolution  Table 10: Supported Display Types  Table 11: USB 3.1 Gen 2/USB 2.0 Port Configuration  Table 12: General Purpose PCI Express 3.0 Lane Configurations.  Table 13: PCI Express Graphics (PEG) Lane Configurations.  Table 14: SATA Port Connections  Table 16: High-speed IO (HSIO) Lane Combinations  Table 17: Storage features  Table 18: BIOS and Software Features  Table 19: General, Special Kontron and Optional Features  Table 20: Electrical Specification  Table 21: Power Supply Control Settings  Table 22: ATX Mode Settings                                               |                            |

| Table 1: Type 6 and COM-bTL6 Functionality  Table 2: Product Number for Commercial Grade Modules (0°C to +60°C operating).  Table 3: Product Number for Industrial Grade Modules (-40°C to +85°C operating).  Table 4: Accessories  Table 5: Technical Data  Table 6: 11th Generation Intel® Core™ Celeron® and Xeon® W Processor Spec  Table 7: Chipset (PCH)  Table 8: System Memory  Table 9: Display Resolution  Table 10: Supported Display Types  Table 11: USB 3.1 Gen 2/USB 2.0 Port Configuration  Table 12: General Purpose PCI Express 3.0 Lane Configurations.  Table 13: PCI Express Graphics (PEG) Lane Configurations.  Table 14: SATA Port Connections  Table 16: High-speed IO (HSIO) Lane Combinations  Table 17: Storage features:  Table 18: BIOS and Software Features  Table 19: General, Special Kontron and Optional Features  Table 20: Electrical Specification  Table 21: Power Supply Control Settings  Table 22: ATX Mode Settings  Table 23: Single Power Supply Mode Settings |                            |

| Table 1: Type 6 and COM-bTL6 Functionality  Table 2: Product Number for Commercial Grade Modules (0°C to +60°C operating).  Table 3: Product Number for Industrial Grade Modules (-40°C to +85°C operating).  Table 4: Accessories  Table 5: Technical Data  Table 6: 11th Generation Intel® Core™ Celeron® and Xeon® W Processor Spec  Table 7: Chipset (PCH)  Table 8: System Memory  Table 9: Display Resolution  Table 10: Supported Display Types  Table 11: USB 3.1 Gen 2/USB 2.0 Port Configuration  Table 12: General Purpose PCI Express 3.0 Lane Configurations.  Table 13: PCI Express Graphics (PEG) Lane Configurations.  Table 14: SATA Port Connections  Table 16: High-speed IO (HSIO) Lane Combinations  Table 17: Storage features  Table 18: BIOS and Software Features  Table 19: General, Special Kontron and Optional Features  Table 20: Electrical Specification  Table 21: Power Supply Control Settings  Table 22: ATX Mode Settings                                               |                            |

| Table 1: Type 6 and COM-bTL6 Functionality.  Table 2: Product Number for Commercial Grade Modules (0°C to +60°C operating)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            |

| Table 28: Country Compliance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Table 29: MTBF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40                                     |

| Table 30: Supported Power States Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44                                     |

| Table 31: GSPI/SPI Hardware Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 46                                     |

| Table 32: SPI Boot Pin Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 47                                     |

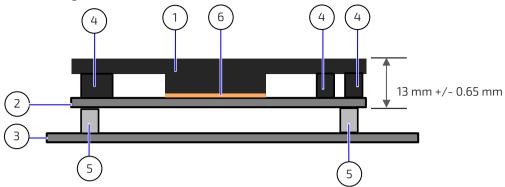

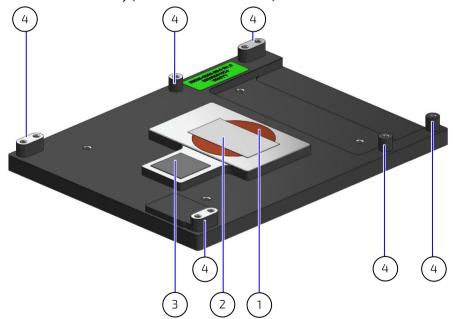

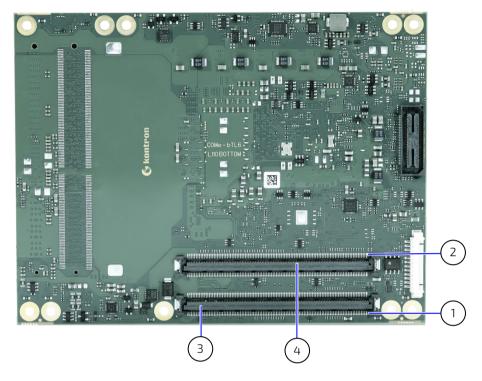

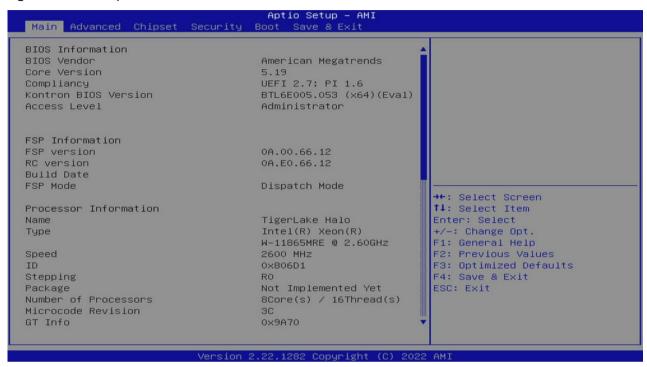

| Table 33: Supported SPI Boot Flash                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 47                                     |