# QSEVEN-Q7ALx2

Doc. User Guide, Rev. 1.0

Doc. ID: 1067-2270

This page has been intentionally left blank

## QSEVEN-Q7ALX2 - USER GUIDE

#### Disclaimer

Kontron would like to point out that the information contained in this user guide may be subject to alteration, particularly as a result of the constant upgrading of Kontron products. This document does not entail any guarantee on the part of Kontron with respect to technical processes described in the user guide or any product characteristics set out in the user guide. Kontron assumes no responsibility or liability for the use of the described product(s), conveys no license or title under any patent, copyright or mask work rights to these products and makes no representations or warranties that these products are free from patent, copyright or mask work right infringement unless otherwise specified. Applications that are described in this user guide are for illustration purposes only. Kontron makes no representation or warranty that such application will be suitable for the specified use without further testing or modification. Kontron expressly informs the user that this user guide only contains a general description of processes and instructions which may not be applicable in every individual case. In cases of doubt, please contact Kontron.

This user guide is protected by copyright. All rights are reserved by Kontron. No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means (electronic, mechanical, photocopying, recording, or otherwise), without the express written permission of Kontron. Kontron points out that the information contained in this user guide is constantly being updated in line with the technical alterations and improvements made by Kontron to the products and thus this user guide only reflects the technical status of the products by Kontron at the time of publishing.

Brand and product names are trademarks or registered trademarks of their respective owners.

©2020 by Kontron Europe GmbH

Kontron Europe GmbH

Gutenbergstrasse 2 85737 Ismaning Germany <u>www.kontron.com</u>

#### Intended Use

THIS DEVICE AND ASSOCIATED SOFTWARE ARE NOT DESIGNED, MANUFACTURED OR INTENDED FOR USE OR RESALE FOR THE OPERATION OF NUCLEAR FACILITIES, THE NAVIGATION, CONTROL OR COMMUNICATION SYSTEMS FOR AIRCRAFT OR OTHER TRANSPORTATION, AIR TRAFFIC CONTROL, LIFE SUPPORT OR LIFE SUSTAINING APPLICATIONS, WEAPONS SYSTEMS, OR ANY OTHER APPLICATION IN A HAZARDOUS ENVIRONMENT, OR REQUIRING FAIL-SAFE PERFORMANCE, OR IN WHICH THE FAILURE OF PRODUCTS COULD LEAD DIRECTLY TO DEATH, PERSONAL INJURY, OR SEVERE PHYSICAL OR ENVIRONMENTAL DAMAGE (COLLECTIVELY, "HIGH RISK APPLICATIONS").

You understand and agree that your use of Kontron devices as a component in High Risk Applications is entirely at your risk. To minimize the risks associated with your products and applications, you should provide adequate design and operating safeguards. You are solely responsible for compliance with all legal, regulatory, safety, and security related requirements concerning your products. You are responsible to ensure that your systems (and any Kontron hardware or software components incorporated in your systems) meet all applicable requirements. Unless otherwise stated in the product documentation, the Kontron device is not provided with error-tolerance capabilities and cannot therefore be deemed as being engineered, manufactured or setup to be compliant for implementation or for resale as device in High Risk Applications. All application and safety related information in this document (including application descriptions, suggested safety measures, suggested Kontron products, and other materials) is provided for reference only.

## **Revision History**

| Revision | Brief Description of Changes | Date of Issue | Author |

|----------|------------------------------|---------------|--------|

| 1.0      | Initial version              |               | CW     |

|          |                              |               |        |

#### Terms and Conditions

Kontron warrants products in accordance with defined regional warranty periods. For more information about warranty compliance and conformity, and the warranty period in your region, visit <a href="http://www.kontron.com/terms-and-conditions">http://www.kontron.com/terms-and-conditions</a>.

Kontron sells products worldwide and declares regional General Terms & Conditions of Sale, and Purchase Order Terms & Conditions. Visit <a href="http://www.kontron.com/terms-and-conditions">http://www.kontron.com/terms-and-conditions</a>.

For contact information, refer to the corporate offices contact information on the last page of this user guide or visit our website <u>CONTACT US</u>.

## **Customer Support**

Find Kontron contacts by visiting: <a href="http://www.kontron.com/support">http://www.kontron.com/support</a>.

## **Customer Service**

As a trusted technology innovator and global solutions provider, Kontron extends its embedded market strengths into a services portfolio allowing companies to break the barriers of traditional product lifecycles. Proven product expertise coupled with collaborative and highly-experienced support enables Kontron to provide exceptional peace of mind to build and maintain successful products.

For more details on Kontron's service offerings such as: enhanced repair services, extended warranty, Kontron training academy, and more visit <a href="http://www.kontron.com/support-and-services/services">http://www.kontron.com/support-and-services/services</a>.

#### **Customer Comments**

If you have any difficulties using this user guide, discover an error, or just want to provide some feedback, contact Kontron Support. Detail any errors you find. We will correct the errors or problems as soon as possible and post the revised user guide on our website.

## **Symbols**

The following symbols may be used in this user guide

#### **ADANGER**

DANGER indicates a hazardous situation which, if not avoided, will result in death or serious injury.

#### **▲**WARNING

WARNING indicates a hazardous situation which, if not avoided, could result in death or serious injury.

### NOTICE

NOTICE indicates a property damage message.

#### **A**CAUTION

CAUTION indicates a hazardous situation which, if not avoided, may result in minor or moderate injury.

#### Electric Shock!

This symbol and title warn of hazards due to electrical shocks (> 60 V) when touching products or parts of products. Failure to observe the precautions indicated and/or prescribed by the law may endanger your life/health and/or result in damage to your material.

#### **ESD Sensitive Device!**

This symbol and title inform that the electronic boards and their components are sensitive to static electricity. Care must therefore be taken during all handling operations and inspections of this product in order to ensure product integrity at all times.

#### **HOT Surface!**

Do NOT touch! Allow to cool before servicing.

#### Laser!

This symbol inform of the risk of exposure to laser beam and light emitting devices (LEDs) from an electrical device. Eye protection per manufacturer notice shall review before servicing.

This symbol indicates general information about the product and the user guide.

This symbol also indicates detail information about the specific product configuration.

This symbol precedes helpful hints and tips for daily use.

## For Your Safety

Your new Kontron product was developed and tested carefully to provide all features necessary to ensure its compliance with electrical safety requirements. It was also designed for a long fault-free life. However, the life expectancy of your product can be drastically reduced by improper treatment during unpacking and installation. Therefore, in the interest of your own safety and of the correct operation of your new Kontron product, you are requested to conform with the following guidelines.

### **High Voltage Safety Instructions**

As a precaution and in case of danger, the power connector must be easily accessible. The power connector is the product's main disconnect device.

#### **A**CAUTION

#### Warning

All operations on this product must be carried out by sufficiently skilled personnel only.

#### **A**CAUTION

### Electric Shock!

Before installing a non hot-swappable Kontron product into a system always ensure that your mains power is switched off. This also applies to the installation of piggybacks. Serious electrical shock hazards can exist during all installation, repair, and maintenance operations on this product. Therefore, always unplug the power cable and any other cables which provide external voltages before performing any work on this product.

Earth ground connection to vehicle's chassis or a central grounding point shall remain connected. The earth ground cable shall be the last cable to be disconnected or the first cable to be connected when performing installation or removal procedures on this product.

### Special Handling and Unpacking Instruction

#### NOTICE

#### ESD Sensitive Device!

Electronic boards and their components are sensitive to static electricity. Therefore, care must be taken during all handling operations and inspections of this product, in order to ensure product integrity at all times.

#### **A**CAUTION

Handling and operation of the product is permitted only for trained personnel within a work place that is access controlled. Follow the "General Safety Instructions for IT Equipment" supplied with the product.

Do not handle this product out of its protective enclosure while it is not used for operational purposes unless it is otherwise protected.

Whenever possible, unpack or pack this product only at EOS/ESD safe work stations. Where a safe work station is not guaranteed, it is important for the user to be electrically discharged before touching the product with his/her hands or tools. This is most easily done by touching a metal part of your system housing.

It is particularly important to observe standard anti-static precautions when changing piggybacks, ROM devices, jumper settings etc. If the product contains batteries for RTC or memory backup, ensure that the product is not placed on conductive surfaces, including anti-static plastics or sponges. They can cause short circuits and damage the batteries or conductive circuits on the product.

## Lithium Battery Precautions

If your product is equipped with a lithium battery, take the following precautions when replacing the battery.

#### **A**CAUTION

#### Danger of explosion if the battery is replaced incorrectly.

- Replace only with same or equivalent battery type recommended by the manufacturer.

- Dispose of used batteries according to the manufacturer's instructions.

## General Instructions on Usage

In order to maintain Kontron's product warranty, this product must not be altered or modified in any way. Changes or modifications to the product, that are not explicitly approved by Kontron and described in this user guide or received from Kontron Support as a special handling instruction, will void your warranty.

This product should only be installed in or connected to systems that fulfill all necessary technical and specific environmental requirements. This also applies to the operational temperature range of the specific board version that must not be exceeded. If batteries are present, their temperature restrictions must be taken into account.

In performing all necessary installation and application operations, only follow the instructions supplied by the present user guide.

Keep all the original packaging material for future storage or warranty shipments. If it is necessary to store or ship the product then re-pack it in the same manner as it was delivered.

Special care is necessary when handling or unpacking the product. See Special Handling and Unpacking Instruction.

## Quality and Environmental Management

Kontron aims to deliver reliable high-end products designed and built for quality, and aims to complying with environmental laws, regulations, and other environmentally oriented requirements. For more information regarding Kontron's quality and environmental responsibilities, visit <a href="http://www.kontron.com/about-kontron/corporate-responsibility/quality-management">http://www.kontron.com/about-kontron/corporate-responsibility/quality-management</a>.

#### Disposal and Recycling

Kontron's products are manufactured to satisfy environmental protection requirements where possible. Many of the components used are capable of being recycled. Final disposal of this product after its service life must be accomplished in accordance with applicable country, state, or local laws or regulations.

### **WEEE Compliance**

The Waste Electrical and Electronic Equipment (WEEE) Directive aims to:

- Reduce waste arising from electrical and electronic equipment (EEE)

- Make producers of EEE responsible for the environmental impact of their products, especially when the product is waste

- Encourage separate collection and subsequent treatment, reuse, recovery, recycling and sound environmental disposal of EEE

- Improve the environmental performance of all those involved during the lifecycle of EEE

Environmental protection is a high priority with Kontron.

Kontron follows the WEEE directive

You are encouraged to return our products for proper disposal.

## **Table of Contents**

| Symbols                                                     | 6  |

|-------------------------------------------------------------|----|

| For Your Safety                                             |    |

| High Voltage Safety Instructions                            | 7  |

| Special Handling and Unpacking Instruction                  | 7  |

| Lithium Battery Precautions                                 |    |

| General Instructions on Usage                               | 8  |

| Quality and Environmental Management                        | 8  |

| Disposal and Recycling                                      |    |

| WEEE Compliance                                             | 8  |

| Table of Contents                                           | 9  |

| List of Tables                                              | 11 |

| List of Figures                                             | 11 |

| 1/ Introduction                                             | 12 |

| 2/ General Safety Instructions                              | 13 |

| Additional Safety Instructions for DC Power Supply Circuits |    |

| 2.1. Electrostatic Discharge (ESD)                          | 14 |

| 2.2. Grounding Methods                                      | 14 |

| 2.3. Requirements IEC 62368-1                               |    |

| 2.4. Instructions for the Lithium Battery                   | 15 |

| 3/ Scope of Delivery                                        | 16 |

| 3.1. Packing List                                           | 16 |

| 3.2. Accessories                                            | 16 |

| 4/ Description                                              | 17 |

| 5/ Specification                                            | 18 |

| 5.1. Block Diagram                                          | 18 |

| 5.2. Module Views                                           | 19 |

| 5.3. Component Technical Data                               | 21 |

| 5.4. Environmental Specification                            | 23 |

| 5.5. Standards and Directives                               | 23 |

| 5.6. Mechanical Specification                               | 25 |

| 5.6.1. Heat Spreader Mechanical Specification               | 26 |

| 5.7. Thermal Management                                     | 27 |

| 5.7.1. Heatspreader Plate and Cooling Solutions             | 27 |

| 5.7.2. Temperature Sensors                                  | 28 |

| 5.8. Power Specification                                    | 29 |

| 5.8.1. Power Supply Specification                           | 29 |

| 5.8.2. Power Supply Voltage Rise Time                       | 29 |

| 5.8.3. Power Supply Voltage Ripple                          | 29 |

| 5.8.4. Input Power Sequencing                               | 30 |

| 5.8.5. Power Management                                     | 30 |

| 5.8.5.1. Power Supply Control and Management Signals        | 31 |

| 6/ Features and Interfaces                                  | 32 |

| 6.1. CAN Bus                                                | 32 |

| 6.2. eMMC (option)                                          | 32 |

| 6.3. Debug Port - JTAG                                      | 32 |

| 6.4. Fast I2C                                               | 32 |

| 6.5. GPIO                                         | 32 |

|---------------------------------------------------|----|

| 6.6. Kontron Security Solution (option)           | 33 |

| 6.7. LPC                                          | 33 |

| 6.8. RTC                                          | 33 |

| 6.9. SDIO                                         | 34 |

| 6.10. SPI                                         | 34 |

| 6.10.1. SPI boot                                  | 34 |

| 6.11. SpeedStep™ Technology                       | 35 |

| 6.12. TPM 2.0 (option)                            | 35 |

| 6.13. UART                                        | 35 |

| 6.14. Watchdog Timer (WDT) - Dual Stage           | 36 |

| 6.14.1. Watchdog Timer Signal                     | 36 |

| 7/ System Resources                               | 37 |

| 7.1. PCI Devices                                  | 37 |

| 7.2. I2C Bus                                      | 37 |

| 7.3. SM Bus                                       | 37 |

| 8/ Connectors                                     | 38 |

| 8.1. Signal Terms                                 | 38 |

| 8.2. Qseven® MXM 230 Pin Assignment               | 39 |

| 9/ Power on                                       | 47 |

| 9.1. Connecting to the Carrier Board              | 47 |

| <b>10</b> / uEFI BIOS                             | 48 |

| 10.1. Starting the uEFI BIOS                      | 48 |

| 10.2. Setup Menus                                 | 49 |

| 10.2.1. Main Setup Menu                           | 49 |

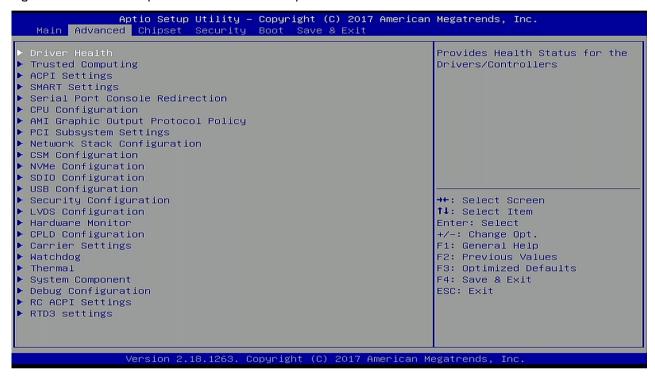

| 10.2.2. Advanced Setup Menu                       | 51 |

| 10.2.3. Chipset Setup Menu                        | 58 |

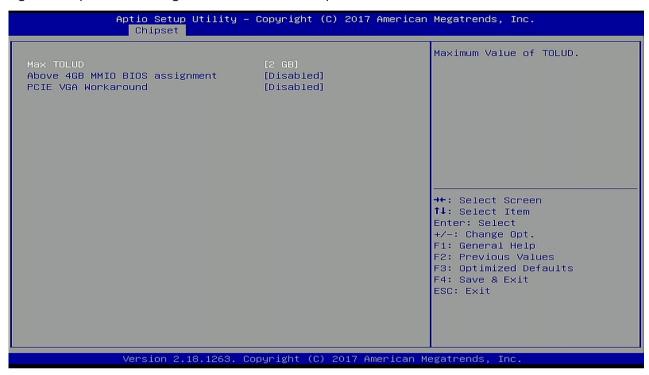

| 10.2.3.1. Chipset> North Bridge                   | 58 |

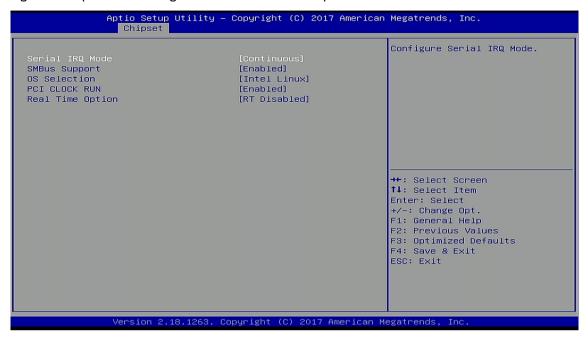

| 10.2.3.2. Chipset > South Bridge                  | 59 |

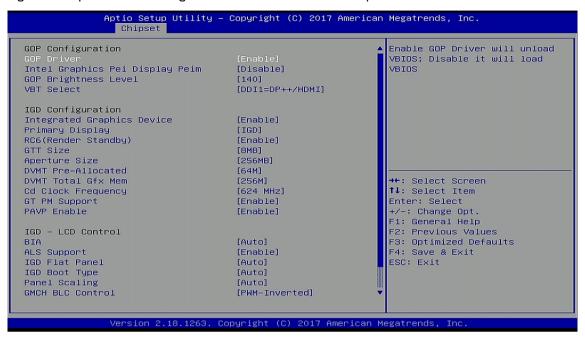

| 10.2.3.3. Chipset> Uncore Configuration           | 60 |

| 10.2.3.4. Chipset> South Cluster Configuration    | 63 |

| 10.2.4. Security Setup Menu                       | 71 |

| 10.2.4.1. Remember the Password                   | 73 |

| 10.2.5. Boot Setup Menu                           | 74 |

| 10.2.6. Save and Exit Setup Menu                  | 76 |

| 10.3. The uEFI Shell                              | 77 |

| 10.3.1. Basic Operation of the uEFI Shell         | 77 |

| 10.3.1.1. Entering the uEFI Shell                 | 77 |

| 10.3.1.2. Exiting the uEFI Shell                  | 77 |

| 10.4. uEFI Shell Scripting                        | 78 |

| 10.4.1. Startup Scripting                         | 78 |

| 10.4.2. Create a Startup Script                   | 78 |

| 10.4.3. Example of Startup Scripts                | 78 |

| 10.4.3.1. Execute Shell Script on other Harddrive | 78 |

| 10.5. Firmware Update                             |    |

| 10.5.1. Updating Procedure                        | 79 |

| Appendix A: List of Acronyms                      |    |

| About Kontron                                     | Ω1 |

## List of Tables

| T-61-2 A                                                                                                                    | 16                   |

|-----------------------------------------------------------------------------------------------------------------------------|----------------------|

| Table 2: Accessory List                                                                                                     | 16                   |

| Table 3: Component Technical Data                                                                                           | 21                   |

| Table 4: Environmental Specification                                                                                        | 23                   |

| Table 5: Standards and Directives                                                                                           | 23                   |

| Table 6: Power Supply Specification                                                                                         | 29                   |

| Table 7: Power Supply Control and Management Signals                                                                        | 31                   |

| Table 8: Supported BIOS Features                                                                                            | 33                   |

| Table 9: SPI Boot Pin Configuration                                                                                         | 34                   |

| Table 10: Supported SPI Boot Flash Types for 8-SOIC Package                                                                 | 34                   |

| Table 11: Dual Staged Watchdog Timer- Time-Out Events                                                                       |                      |

| Table 12: I2C Bus Port Address                                                                                              | 37                   |

| Table 13. SMBus Address                                                                                                     |                      |

| Table 14: Qseven® Signal Terms                                                                                              |                      |

| Table 15: QSEVEN® Module Connector Pin Assignment of Bottom Side                                                            | 39                   |

| Table 16: QSEVEN® Module Connector Pin Assignment of Top Side Row                                                           | 43                   |

| Table 17: Navigation Hot Keys in the Legend Bar                                                                             | 48                   |

| Table 18: Main Setup Menu Sub-screens and Functions Example                                                                 | 50                   |

| Table 19: Advanced Setup menu Sub-screens and Functions Example                                                             |                      |

| Table 20: Chipset Set > North Bridge Sub-screens and Function                                                               | 58                   |

| Table 21: Chipset Set> South Bridge Sub-screens and Functions                                                               |                      |

| Table 22: Chipset Set> Uncore Configuration Sub-screens and Functions                                                       | 61                   |

| Table 23: Chipset>South Cluster Configuration Sub-screens and Functions                                                     |                      |

| Table 24: Security Setup Menu Initial Screen                                                                                | 71                   |

| Table 25: Boot Setup Menu Sub-screens and Functions                                                                         |                      |

| Table 26: Save and Exit Setup Menu Sub-screens and Functions                                                                | 76                   |

| Table 27: List of Acronyms                                                                                                  | 80                   |

|                                                                                                                             |                      |

| List of Figures                                                                                                             |                      |

| List of Figures Figure 1: QSEVEN Module                                                                                     | 17                   |

| <del>-</del>                                                                                                                |                      |

| Figure 1: QSEVEN Module                                                                                                     | 18                   |

| Figure 1: QSEVEN ModuleFigure 2 : Block Diagram Q7ALx2 Module                                                               | 18<br>19             |

| Figure 1: QSEVEN Module<br>Figure 2 : Block Diagram Q7ALx2 Module<br>Figure 3 : Top Side View Q7ALx2                        | 18<br>19<br>20       |

| Figure 1: QSEVEN ModuleFigure 2: Block Diagram Q7ALx2 ModuleFigure 3: Top Side View Q7ALx2Figure 4: Bottom Side View Q7ALx2 | 18<br>20<br>25       |

| Figure 1: QSEVEN Module                                                                                                     | 18<br>20<br>25       |

| Figure 1: QSEVEN Module                                                                                                     | 18<br>20<br>25<br>25 |

| Figure 1: QSEVEN Module                                                                                                     | 1820252526           |

| Figure 1: QSEVEN Module                                                                                                     | 1820252626           |

| Figure 1: QSEVEN Module                                                                                                     | 18202525262627       |

| Figure 1: QSEVEN Module                                                                                                     |                      |

### 1/ Introduction

This user guide describes the Qseven® Q7ALx2 module from Kontron. The Q7ALx2 is an off-the-shelf module designed to meet the Qseven® standard. The use of the Qseven® Q7ALx2 module requires basic knowledge of PC hardware and software. This user guide focuses on describing the Q7ALx2's special features and is not intended to be a standard PC textbook.

Before powering on the Q7ALx2 module, Kontron recommends new users to read and observe Chapter 2/: General Safety Instructions, and study the power on procedure in Chapter 9/: Power on.

The configuration and setup of the Qseven® Q7ALx2 module is automatic, or performed manually by the user within the BIOS setup.

Latest revision of this user guide, datasheet, BIOS, drivers and BSPs (Board Support Packages) are available for downloaded from Kontron's Web Page.

## 2/ General Safety Instructions

Please read this passage carefully and take careful note of the instructions, which have been compiled for your safety and to ensure to apply in accordance with intended regulations. If the following general safety instructions are not observed, it could lead to injuries to the operator and/or damage of the product; in cases of non-observance of the instructions Kontron Europe is exempt from accident liability, this also applies during the warranty period.

The product has been built and tested according to the basic safety requirements for low voltage (LVD) applications and has left the manufacturer in safety-related, flawless condition. To maintain this condition and to also ensure safe operation, the operator must not only observe the correct operating conditions for the product but also the following general safety instructions:

- The product must be used as specified in the product documentation, in which the instructions for safety for the product and for the operator are described. These contain guidelines for setting up, installation and assembly, maintenance, transport or storage.

- The on-site electrical installation must meet the requirements of the country's specific local regulations.

- If a power cable comes with the product, only this cable should be used. Do not use an extension cable to connect the product.

- To guarantee that sufficient air circulation is available to cool the product, please ensure that the ventilation openings are not covered or blocked. If a filter mat is provided, this should be cleaned regularly. Do not place the product close to heat sources or damp places. Make sure the product is well ventilated.

- Only connect the product to an external power supply providing the voltage type (AC or DC) and the input power (max. current) specified on the Kontron Product Label and meeting the requirements of the Limited Power Source (LPS) and Power Source (PS2) of UL/IEC 62368-1.

- Only products or parts that meet the requirements for Power Source (PS1) of UL/IEC 62368-1 may be connected to the product's available interfaces (I/O).

- Before opening the product, make sure that the product is disconnected from the mains.

- Switching off the product by its power button does not disconnect it from the mains. Complete disconnection is only possible if the power cable is removed from the wall plug or from the product. Ensure that there is free and easy access to enable disconnection.

- The product may only be opened for the insertion or removal of add-on cards (depending on the configuration of the product). This may only be carried out by qualified operators.

- If extensions are being carried out, the following must be observed:

- all effective legal regulations and all technical data are adhered to

- b the power consumption of any add-on card does not exceed the specified limitations

- the current consumption of the product does not exceed the value stated on the product label.

- Only original accessories that have been approved by Kontron Europe can be used.

- Please note: safe operation is no longer possible when any of the following applies:

- the product has visible damages or

- the product is no longer functioning In this case the product must be switched off and it must be ensured that the product can no longer be operated.

- Handling and operation of the product is permitted only for trained personnel within a work place that is access controlled.

- CAUTION: Risk of explosion if the battery is replaced incorrectly (short-circuited, reverse-poled, wrong battery type). Dispose of used batteries according to the manufacturer's instructions.

- This product is not suitable for use in locations where children are likely to be present

## Additional Safety Instructions for DC Power Supply Circuits

- To guarantee safe operation, please observe that:

- the external DC power supply must meet the criteria for LPS and PS2 (UL/IEC 62368-1)

- no cables or parts without insulation in electrical circuits with dangerous voltage or power should be touched directly or indirectly

- a reliable protective earthing connection is provided

- a suitable, easily accessible disconnecting device is used in the application (e.g. overcurrent protective device), if the product itself is not disconnect able

- a disconnect device, if provided in or as part of the product, shall disconnect both poles simultaneously

- interconnecting power circuits of different products cause no electrical hazards

- A sufficient dimensioning of the power cable wires must be selected according to the maximum electrical specifications on the product label as stipulated by EN62368-1 or VDE0100 or EN60204 or UL61010-1 regulations.

### 2.1. Electrostatic Discharge (ESD)

A sudden discharge of electrostatic electricity can destroy static-sensitive devices.

Proper packaging and grounding techniques are necessary precautions to prevent damage. Always take the following precautions:

- 1. Transport ESD-sensitive products in ESD-safe containers such as boxes or bags.

- 2. Keep electrostatic sensitive parts in their containers until they arrive at the ESD-safe workplace.

- 3. Always be properly grounded when touching sensitive products, components, or assembly.

- 4. Store ESD-sensitive products in protective packaging or on antistatic mats.

#### 2.2. Grounding Methods

To avoid electrostatic damage, observe the following grounding guidelines:

- Cover workstations with approved antistatic material. Always wear a wrist strap connected to the workplace. Always use properly grounded tools and equipment.

- 2. Use antistatic mats, heel straps, or air ionizers for more protection.

- 3. Always handle electrostatically sensitive components by their edge or by their casing.

- 4. Avoid contact with pins, leads, or circuitry.

- 5. Switch off power and input signals before inserting and removing connectors or connecting test equipment.

- 6. Keep work area free of non-conductive materials such as ordinary plastic assembly aids and Styrofoam.

- 7. Use only field service tools that are conductive, such as cutters, screwdrivers, and vacuum cleaners.

- **8.** Always place drives and boards PCB-assembly-side down on the foam.

#### 2.3. Requirements IEC 62368-1

Users of the Q7ALx2 module must evaluate the end product to ensure the requirements of the IEC 62368-1 safety standard are met:

- The module must be installed in a suitable mechanical, electrical and fire enclosure.

- The module in its enclosure must be evaluated for temperature and airflow considerations.

- For interfaces having a power pin such as external power or fan, ensure that the connectors and wires are suitably rated.

- All connections from or to the Module shall be with Safety Extra Low Voltage (SELV) circuits only.

- Wires have suitable rating to withstand the maximum available power.

- The enclosure of any peripheral device fulfills the fire protecting requirements of IEC 62368-1.

## 2.4. Instructions for the Lithium Battery

The O7ALx2 module is supported via a lithium battery on a separate carrier board. When replacing a lithium battery, only use the same or equivalent type or a replacement recommended by the manufacturer. Follow the replacement precautions stated below.

#### **A**CAUTION

Danger of explosion, when replaced with wrong type of battery. Replace only with the same or equivalent battery type recommended by the manufacturer. The lithium battery type must be UL recognized.

After removing the lithium battery, dispose of the lithium battery according to the regulations within your region.

Do not dispose of lithium batteries in general trash collection. Dispose of the battery according to the local regulations dealing with the disposal of these special materials, (e.g. to the collecting points for dispose of batteries).

## 3/ Scope of Delivery

## 3.1. Packing List

Check that your delivery is complete, and contains the item(s) below (according to the ordered configuration). If you discover damaged or missing item(s), contact your dealer.

Table 1: Packing List

| Delivered Part | Part Description                                             |

|----------------|--------------------------------------------------------------|

| Q7ALx2         | Qseven® module board with Intel x86 SoC and on-module memory |

Note: The above packing list is for standard single box package only.

#### 3.2. Accessories

The following accessories are available for the Q7ALx2.

Table 2: Accessory List

| Part Name                     | SAP Number      | Part Description                                          |

|-------------------------------|-----------------|-----------------------------------------------------------|

| Heatspreader Plate Commercial | 81004-0000-99-1 | Heatspeader to attach to commercial Qseven® Q7ALx2 module |

| Heatspreader Plate Industrial | 81005-0000-99-1 | Heatspeader to attach to industrial Qseven® Q7ALx2 module |

| Qseven-Eval Carrier           | 81100-000-00-0  | Qseven® 2.1 pin-out Evaluation carrier board              |

## 4/Description

The Oseven® O7ALx2module is an off-the-shelf module designed to meet the Oseven® Specification Rev. 2.1.

The Q7ALx2 includes all the components of a common PC (Intel x86 SoC, on-module system memory, eMMC Flash memory expansion and extensive interfaces.) on a small form factor board (70 mm x 70 mm) designed for mounting on a carrier board using the Qseven® (MXM) connector. The carrier board powers the Q7ALx2 and the carrier board interfaces connect to the end application.

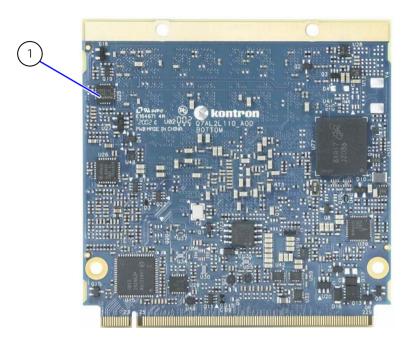

Figure 1: QSEVEN Module

The main Oseven-07ALx2 features are:

- Intel® Atom x5 E3950, E3940, E3930 and mobile Celeron N3350/4200 with integrated chipset

- Qseven® form factor (70 mm x 70 mm)

- Oseven® connector complies to Oseven® specification Rev 2.1

- Up to 8 GByte LPDDR4 memory down

- From 32 GByte (pSLC) /up to 64 GB (MLC) eMMC 5.1 Flash (option)

- 2x SATA 6 Gb/s

- 4x PCle x1, Gen 2

- 1x GbE LAN

- 2x USB 3.0 (QSEVEN port 0,1)

- 4x USB 2.0 Host (QSEVEN port 2, 3, 4, 5)

- 1x USB 2.0 OTG (QSEVEN port 1) using switch of full functional OTG

- 2x Display (1x eDP and 1x DP or HDMI)

- ► 1x SDIO

- 1x SPI external Boot (SPI0)

- 1x SPI for generic devices (SPI1)

- > 1x HDA Audio / I2S Audio (muxed)

- 2x I2C interfaces

- 1x SMB interface

- 1x UART interfaces

- 8x GPIO's / LPC (muxed)

- 1x CAN Bus interface (option)

## 5/ Specification

## 5.1. Block Diagram

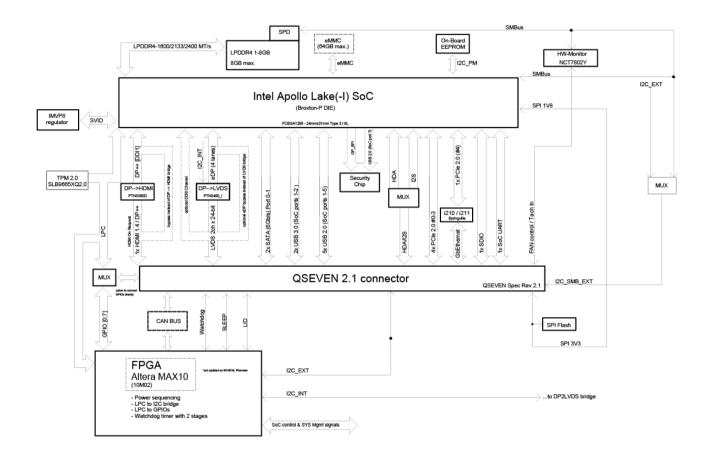

Figure 2: Block Diagram Q7ALx2 Module

Note: Dashed outline is optional

## 5.2. Module Views

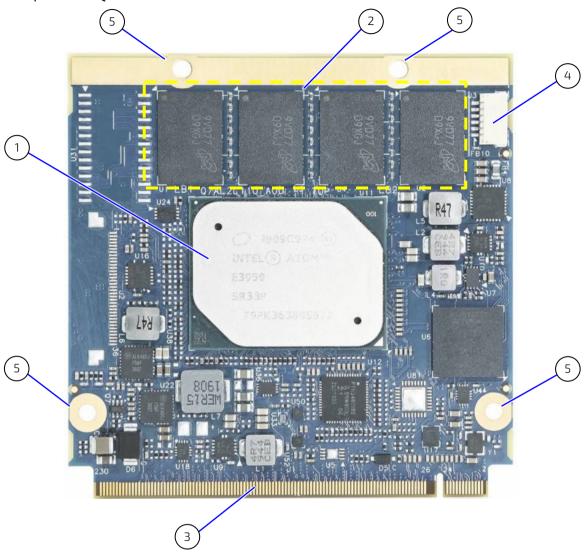

Figure 3: Top Side View Q7ALx2

- 1 SOC

- 2 Memory down

- 3 Qseven® connector (top side)

- CPLD connector

- 5 4x Mounting points

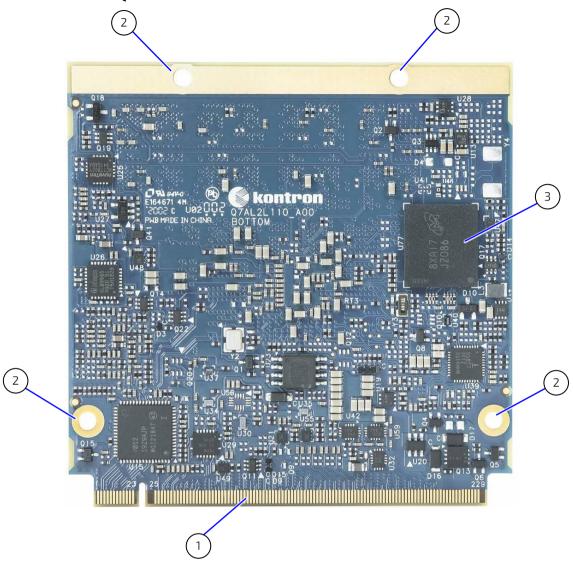

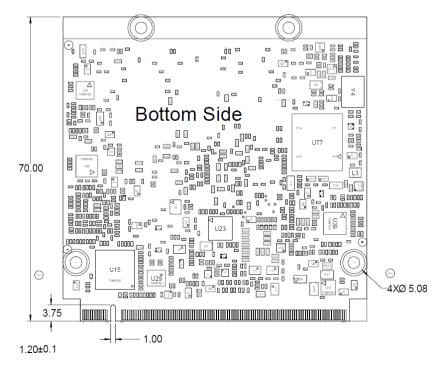

Figure 4 : Bottom Side View Q7ALx2

- 1 Qseven® connector (bottom side) 3 eMMC

- 2 4x Mounting points

## 5.3. Component Technical Data

The table below summarizes the Q7ALx2 module's main component technical features:

Table 3: Component Technical Data

| Q7ALx2 Module                                      |                                                                                                                                                                                                                                                                                          |  |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Form Factor                                        | Qseven® module standardized form factor (70 mm x 70 mm)                                                                                                                                                                                                                                  |  |

| Processor                                          |                                                                                                                                                                                                                                                                                          |  |

| System On Chip<br>(SOC)                            | Embedded processors based on Intel x86 SoC with integrated chipset:  Industrial Grade (@ -40°C to 85°C):  Intel Atom x5 E3930, 2 Cores, 1.8 GHz, 6,5 W                                                                                                                                   |  |

|                                                    | <ul> <li>Intel Atom x5 E3940, 4 Cores, 1.8 GHz, 9,5 W</li> <li>Intel Atom x7 E3950, 4 Cores, 2.0 GHz, 12 W</li> <li>Commercial Grade (0°C to 60°C):</li> </ul>                                                                                                                           |  |

|                                                    | <ul> <li>Intel Mobile Celeron N3350 2 Cores, 2.4 GHz, 6 W</li> <li>Intel Mobile Celeron N4200 2 Cores, 2.5 GHz, 6 W</li> </ul>                                                                                                                                                           |  |

| Memory                                             | Line to (iv. LDDDD// 1.2 VDDAMe                                                                                                                                                                                                                                                          |  |

| System Memory                                      | <ul> <li>Up to 4x LPDDR4 1.2 V DRAMs</li> <li>Single channel</li> <li>Up to 8 GBytes (1 GB to 8 GB)</li> <li>2400 MT/s</li> </ul>                                                                                                                                                        |  |

| eMMC Storage                                       | 2 GByte to 32 GByte (pSLC) eMMC 5.1 Flash                                                                                                                                                                                                                                                |  |

| (option)                                           | or  2 GByte to 64 GByte (MLC) eMMC 5.1 Flash                                                                                                                                                                                                                                             |  |

| Controller                                         |                                                                                                                                                                                                                                                                                          |  |

| Embedded<br>Controller                             | FPGA (MAX10) controller for embedded feature set and logic control                                                                                                                                                                                                                       |  |

| H/W Status<br>Monitor                              | Nuvoton NCT7802Y hardware monitor supports:  SM Bus connection to SoC  PWM and Tach interface to external fan  Temperature measurements (2x external thermal diodes and 1x internal sensor)  Analog/Digital measurements on V_RTC, VCC and VCC_SB                                        |  |

| Complex<br>Programmable<br>Logic Devices<br>(CPLD) | <ul> <li>CPLD (MAX10) controller supports:         <ul> <li>Power Sequencing</li> <li>Status and control signal level shifting to allow signals routed to Qseven® connector to comply with Qseven® Specifications</li> <li>LPC to UART bridge to provide 4-wire UART</li></ul></li></ul> |  |

| Watchdog                                           | Dual Staged Watchdog timer supported by:  Watchdog time out (WDOUT)  Watchdog trigger(WDTRIG#)                                                                                                                                                                                           |  |

| Software                                                                     |                                                                                          |  |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|

|                                                                              | On heard 120 Mb CDI flack for DIOC storage                                               |  |

| BIOS                                                                         | On-board 128 Mb SPI flash for BIOS storage                                               |  |

| Operating System                                                             | ▶ Windows® 10 Enterprise 64 bit                                                          |  |

| Support                                                                      | Windows 10 IoT 64 bit                                                                    |  |

|                                                                              | Linux Yocto 64-bit                                                                       |  |

| _                                                                            |                                                                                          |  |

| I/O functions on Qseven® connector                                           |                                                                                          |  |

| PCle                                                                         | 4x PCIe Gen 2 (5 GT/s), lanes configured as:                                             |  |

|                                                                              | <ul><li>4 x1 (4 PCIe links x 1 wide)</li><li>1 x4 (1 PCIe link x 4 wide)</li></ul>       |  |

|                                                                              | 1 A4 (11 Cle tillik A 4 Wide)                                                            |  |

|                                                                              | Note 1: Implement the PCIe links and support signals as per the Qseven® Specification.   |  |

|                                                                              | Note 2:The lane may not be configured as 2x2                                             |  |

|                                                                              | Note 3: PCle mapping is not supported in standard BIOS                                   |  |

| CATA                                                                         | 2. CATA Con 2 links (6Ch /s)                                                             |  |

| SATA                                                                         | 2x SATA Gen 3 links (6Gb/s)                                                              |  |

| GbE LAN                                                                      | 1x GBE port (using Intel i210IT/i211AT Ethernet controller)                              |  |

| USB                                                                          | 2x USB 3.0 (USB 3.0 or USB 2.0 compatible)                                               |  |

|                                                                              | 4x USB 2.0                                                                               |  |

|                                                                              | 1x USB OTG (USB 2.0 host or client operation)                                            |  |

| HDA                                                                          | 1x HDA audio (muxed with I2S interface)                                                  |  |

| I2S                                                                          | 1x Inter-IC Sound (I2S) interface (muxed with HDA interface)                             |  |

| Serial Port                                                                  | 1x 4-wire UART interface (TX, RX, CTS, RTS) at 3.3 VDC (supported by the MAX10 FPGA)     |  |

| SPI                                                                          | 1x fast SPI interface from primary SPI chip for external boot from Carrier BIOS SPI chip |  |

|                                                                              | 1x SPI interface as secondary SPI interface for generic SPI devices on the carrier board |  |

| CAN                                                                          | 1x CAN bus V2.0 interface (option)                                                       |  |

| I2C                                                                          | 2x I2C Interfaces (1x standard and 1x muxed with SMB)                                    |  |

| GPIO                                                                         | 8x General Purpose Input/Output (GPIOs) configurable in BIOS (muxed with LPC bus)        |  |

| SDI0                                                                         | 1x SDIO interface with the Qseven® connector                                             |  |

| LVDS                                                                         | Dual channel using eDP2LVDS or eDP + DP                                                  |  |

| On-module Connecto                                                           | ors                                                                                      |  |

| CPLD                                                                         | 1x CPLD,6-pin connector ( used for JTAG)                                                 |  |

|                                                                              | 1.0 0.0000 220 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                           |  |

| Qseven®                                                                      | 1x Qseven® MXM, 230-pin connector (used for interfaces, control and power)               |  |

| Power                                                                        |                                                                                          |  |

| Power Supply                                                                 | VCC = 5 VDC +/- 5%                                                                       |  |

| i owei Juppty                                                                | VCC_SB = 5 VDC +/- 5%                                                                    |  |

|                                                                              | VCC_RTC = 3 VDC (Range: 2.4 VDC to 3.3 VDC)                                              |  |

| Davier                                                                       | Power saving supports C-states                                                           |  |

| PowerPower saving supports C-statesManagementoC0, C1, C6, C7, C8, C9 and C10 |                                                                                          |  |

|                                                                              | ► Wake on LAN (WOL)                                                                      |  |

|                                                                              |                                                                                          |  |

| LID/SLeep/Batlow                                                             | Supported                                                                                |  |

| Signal                                                                       |                                                                                          |  |

|                                                                              |                                                                                          |  |

| Display                                                | Display |                                                                                                                                                                     |  |  |

|--------------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Digital Displays                                       |         | Up to two independent digital displays using "DDI0" and "DDI1" from the SoC:  DDI0 – eDP (no LVDS only shares Qseven® connector pin with LVDS)  DDI1 - DP++ or HDMI |  |  |

| DDI0                                                   | eDP     | eDP interface is DDI0 from SoC (Resolution: 3840x2160 @60Hz)                                                                                                        |  |  |

| DDI1 HDMI Dual Mode HDMI (Resolution: 3840x2160 @30Hz) |         | Dual Mode HDMI (Resolution: 3840x2160 @30Hz)                                                                                                                        |  |  |

| DP++                                                   |         | DP++ interface is DDI1 from SoC (Resolution: 4096x2160 @60Hz)                                                                                                       |  |  |

| Security                                               |         |                                                                                                                                                                     |  |  |

| ТРМ                                                    |         | TPM 2.0 (option)                                                                                                                                                    |  |  |

| Kontron Security Solution                              |         | Approtect supported (option)                                                                                                                                        |  |  |

## 5.4. Environmental Specification

Table 4: Environmental Specification

| Environmental     |                                                             |                |

|-------------------|-------------------------------------------------------------|----------------|

| Temperature       | Commercial grade                                            | 0°C to +60°    |

| (operating)       | Industrial grade (E2):                                      | -40°C to +85°  |

| Temperature       | Commercial grade                                            | -40°C to +85°C |

| (non-operating)   | Industrial grade                                            |                |

| Relative Humidity | 93%, at +40°C, non-condensing (according to IEC 60068-2-78) |                |

| Vibration         | According to IEC/EN60068-2-64                               |                |

| Shock             | According to IEC/EN60068-2-27                               |                |

## 5.5. Standards and Directives

The Qseven® Q7ALx2 module complies with the following Standards and Directives.

Table 5: Standards and Directives

| CE                     |                  |                                                                                                                                                                                                                                                                              |            |

|------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| National Certification |                  | CE Marking Directive                                                                                                                                                                                                                                                         | 93/68/EEC  |

|                        |                  | Low Voltage Directive (LVD)                                                                                                                                                                                                                                                  | 2006/95/EC |

| EMC/EMI                |                  |                                                                                                                                                                                                                                                                              |            |

| Emission               | EN 55032 Class B | Test conducted in standard available chassis with Q7 carrier board.  Electromagnetic compatible – Emission standard for information technology equipment (ITE). External test in certified test laboratory and declaration of conformity written by Kontron Technology only. |            |

| Immunity               | EN 61000-6-1     | Test conducted in standard available chassis with Q7 carrier board. Electromagnetic compatible – Generic immunity standard Part1: Residential, commercial and light industrial environment. Internal test and declaration of conformity written by Kontron Technology only.  |            |

| Safety    |                                                                                                                                                                                                                                                        |                                                                                                             |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|

| Europe    | IEC 62368-1                                                                                                                                                                                                                                            | Component recognition Audio/video, information and communication technology equipment – Safety requirements |  |

| USA &     | UL62368-1                                                                                                                                                                                                                                              | teermotogy equipment Surety requirements                                                                    |  |

| Canada    | CAN/CSA C22.2 No. 62368-1                                                                                                                                                                                                                              |                                                                                                             |  |

| Environme | Environment                                                                                                                                                                                                                                            |                                                                                                             |  |

| WEEE      | Compliant with the Waste Electrical and Electronic Equipment (WEEE) 2012/19/EU directive; to reduce waste of electrical and electronic equipment, encourage recycling and environmental disposal and increase the environmental awareness of producers |                                                                                                             |  |

| RoHS II   | II Compliant with the Restriction of Hazardous Substances (RoHS) 2011/65/EU directive or the late status thereof, to reduce hazardous substances in electrical and electronic equipment                                                                |                                                                                                             |  |

| REACH     | Compliant with the Registration, Evaluation, Authorization and Restriction of Chemicals (REACH) Regulation No. 1907/2006 to identify the intrinsic properties of chemical substances earlier                                                           |                                                                                                             |  |

## 5.6. Mechanical Specification

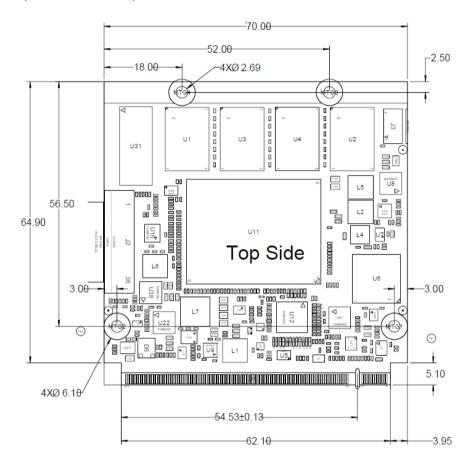

Figure 5: Q7ALx2 Top Side Mechanical Specification (measurement in mm)

Figure 6: Q7ALx2 Bottom Side Mechanical Specification (measurement in mm)

## 5.6.1. Heat Spreader Mechanical Specification

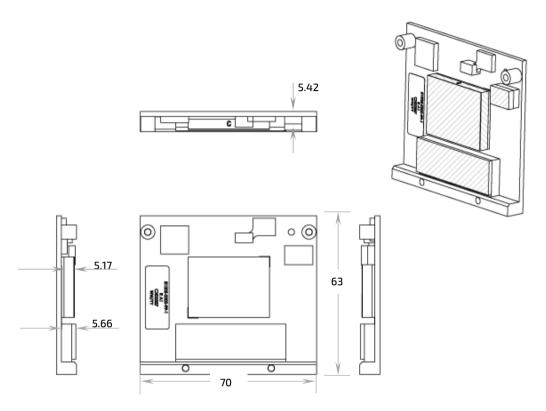

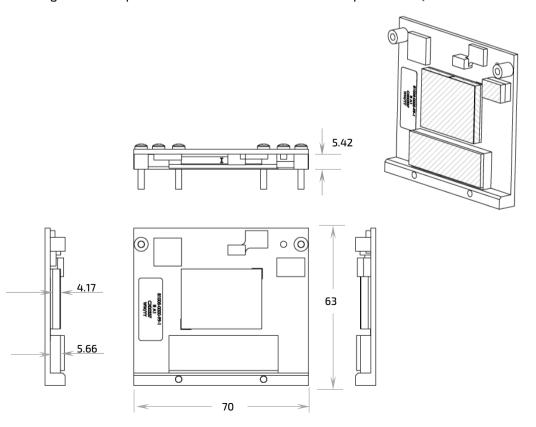

Figure 7: Heat Spreader for Commercial Grade Mechanical Specification (measurement in mm)

Figure 8: Heat Spreader for Industrial Grade Mechanical Specification (measurement in mm)

### 5.7. Thermal Management

### 5.7.1. Heatspreader Plate and Cooling Solutions

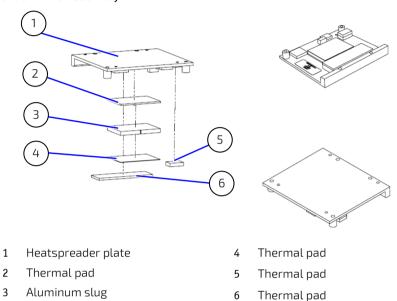

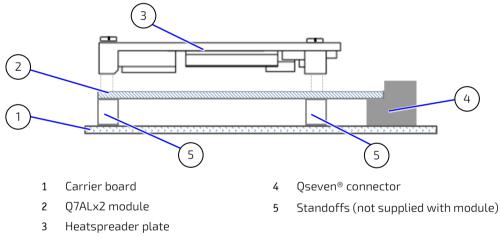

A heatspreader plate assembly is available for the Q7ALx2. The heatspreader plate is NOT a heat sink. The heatspreader plate is a Qseven® standard thermal interface to accompany a heat sink or external cooling device(s).

The aluminum slugs and thermal pads on the underside of the heatspreader plate act as thermal interfaces between the heatspreader plate and the major heat-generating components on the Q7ALx2 module. Approximately 80 % of the module's dissipated power is conducted to the heatspreader plate and can be removed by the cooling solution.

Figure 9: Heatspreader Plate Assembly

An external cooling device must be used to maintain the heatspreader plate at the specified operating temperature. Under worst-case conditions, the cooling device must maintain an ambient air temperature and the heatspreader plate temperature, on any spot of the heatspreader's surface, must remain under the temperature grade's maximum specification of:

- ▶ 60°C for commercial grade modules

- > 75°C for extended temperature grade modules

- ▶ 85°C for industrial temperature grade module

#### **ACAUTION**

#### Hot Surface

A Heatspreader plate or heatsink can get hot. To avoid burns and personal injury:

- Do not touch the when the product is operating

- Allow the product to cool before handling

- Wear protective gloves

- · Switch off the product when not in use

#### **ACAUTION**

Operate only with an external cooling solution

To maintain the surface temperature of the heatspreader plate under the maximum temperature specified, an external cooling device such as a heatsink must be used.

## 5.7.2. Temperature Sensors

The Hardware Monitor (HWM) chip (Nuvoton NCT802Y) uses an on-chip temperature sensor to measure the module's temperature. This measurement is referred to as the "module temperature" in the BIOS setup menu (Advanced>H/W Monitor). The HWM uses the SMBus interface, see Table 13. SMBus Address.

Figure 10: HWM with Temperature Sensor

1 HWM Chip - measures "module temperature"

For documentation and CAD drawings of heatspreader plate and cooling solutions, refer to Kontron's <u>Customer Section</u>.

### 5.8. Power Specification

The Q7ALx2 module receives power from a carrier board via the Qseven® connector. The Q7ALx2 must be connected to a carrier board to power on.

#### **ACAUTION**

The Qseven® module is powered on by connecting to a carrier board using the Qseven® connector. Before connecting the module's Qseven® connector to the carrier board's corresponding connector, switched off and disconnected the carrier board from the main power supply. Failure to disconnect the main power supply could result in personal injury and damage to the module and/or carrier board.

## 5.8.1. Power Supply Specification

As defined by the Qseven® specification, the Q7ALx2 module is supplied with power using 5 VDC VCC pins on the Qseven® connector. A single +5 VDC input power rail drives the Q7ALx2 module. Additionally, two optional power rails supply other supported supply voltages such as +5 VDC standby and 3 VDC Real Time Clock (RTC). The RTC battery cell located on the carrier board provides the RTC voltage.

Table 6: Power Supply Specification

| Supply Voltage (VCC)     | 5 VDC                                                          |  |

|--------------------------|----------------------------------------------------------------|--|

| Standby Voltage (VCC_SB) | 5 VDC ±5 %                                                     |  |

| RTC Voltage (VCC_RTC)    | 3 VDC ( Range: 2.4 VDC to 3.3 VDC)                             |  |

| Ground (GND)             | Power Ground                                                   |  |

| Input Current            | out Current 0.5 A per input voltage pin (max.)                 |  |

| Module Power             | 12W (when supplied with the minimum input voltage level (max.) |  |

#### **A**CAUTION

Only connect the product to an external power supply providing the voltage type (AC or DC) and the input power (max. current) specified on the Kontron Product Label/within this user guide and meeting the requirements of the Limited Power Source (LPS) and Power Source (PS2) of UL/IEC 62368-1

## 5.8.2. Power Supply Voltage Rise Time

The input voltage rise time is  $0.1 \, \text{ms}$  to  $20 \, \text{ms}$  from input voltage  $\leq 10\%$  to nominal input voltage. To comply with the ATX specification there must be a smooth and continuous ramp up of each DC input voltage from 10% to 90% of the DC input voltage final set point.

#### 5.8.3. Power Supply Voltage Ripple

The maximum power supply voltage ripple for the input voltage range (+4.75 VDC to 5.25 VDC) is 50 mV peak-to-peak. The voltage ripple must not cause the input voltage range to be exceeded.

### 5.8.4. Input Power Sequencing

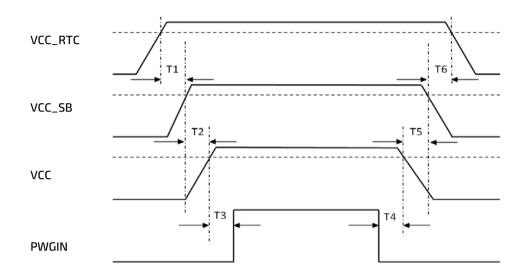

The following figure illustrates the Q7ALx2 module's inputs power start and stop sequence requirements.

Figure 11: Input Power Start and Stop Sequence

PWGIN is an active high input for the Qseven® module and indicate that the all the power rails on the carrier board are ready for use.

#### Start sequence

- VCC\_RTC must come up at the same time or before VCC\_SB comes up (T1)

- VCC\_SB must come up at the same time or before VCC comes up (T2)

- PWGIN must be active at the same time or after VCC comes up (T3)

#### Stop Sequence

- PWGIN must be inactive at the same time or before VCC goes down (T4)

- VCC must go down at the same time or before VCC\_SB goes down (T5)

- VCC\_SB must go down at the same time or before VCC\_RTC goes down (T6)

### 5.8.5. Power Management

Power management options are available within the BIOS setup. The Q7ALx2 implements the Advanced Configuration and Power Interface (ACPI) ACPI 3.0 hardware specification to control typical features such as power button and suspend states.

If power is removed, 5 VDC can be applied to VCC\_SB pins (pins 205 and 206) to support the suspend-states:

- Suspend-to-Disk (S4)

- Soft-off state (S5)

Implementing the wake-up event (S0) requires a connection to power, as the module will be started.

## 5.8.5.1. Power Supply Control and Management Signals

Power supply control settings are set in the BIOS setup menus and enable the module to shut down, rest and wake from standby.

Table 7: Power Supply Control and Management Signals

| Signal   | Pin | Description                                                                                                                                                                                                                       | I/O Type             | IOL/ IIL | I/<br>0 |

|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------|---------|

| PWRBTN#  | 20  | Power button: this signal is a low active input and triggered on the falling edge                                                                                                                                                 | CMOS<br>3.3V Standby | ≥10 mA   | I       |

| PWGIN#   | 26  | Power good input: this high active input for the Qseven® module indicates that all power rails located on the carrier board are ready for use.                                                                                    | CMOS<br>5V           | ≥ 4 mA   | I       |

| RSTBTN#  | 28  | Reset button: this input may be driven active low by external circuitry to reset the Qseven® module.                                                                                                                              | CMOS<br>3.3V         | ≥ 10 mA  | I       |

| BATLOW#  | 27  | Battery low: this signal may be driven active low by external circuitry to signal that the system battery is low or may be used to signal some other external battery management event.                                           | CMOS<br>3.3V Suspend | ≥ 10 mA  | I       |

| Wake#    | 17  | Wake Event: this may be driven active low by external circuitry to signal an external wake-up event.                                                                                                                              | CMOS<br>3.3V Suspend | ≥ 10 mA  | I       |

| SUS_S3#  | 18  | S3 State: this signal shuts off power to all runtime system components that are not maintained during S3 (Suspend to Ram), S4 or S5 states. The signal SUS_S3# is necessary in order to support the optional S3 cold power state. | CMOS<br>3.3V Suspend | ≥1 mA    | 0       |

| SUS_S5#  | 16  | S5 State: This signal indicates S4 or S5 (Soft Off) state.                                                                                                                                                                        | CMOS<br>3.3V Suspend | ≥ 1 mA   | 0       |

| SLP_BTN# | 21  | Sleep button: this low active signal transitions the module into the sleep state or to wake up the system up. This signal is triggered on falling edge. (Pin shared with GPIO)                                                    | CMOS<br>3.3V Suspend | ≥ 10 mA  | I       |

| LID_BTN# | 22  | LID button: this low active signal detects a LID switch and brings the module into the sleep state or wakes up the module again.  Open/Close state may be software configurable. (Pin shared with GPIO)                           | CMOS<br>3.3V Suspend | ≥ 10 mA  | I       |

The SUS\_S3# signal must be able to enable the carrier board's power rails generated out of the VCC power rail.

### 6/ Features and Interfaces

#### 6.1. CAN Bus

The CAN Bus interface is compliant with the CAN Bus V 2.0 specification and implemented via a LPC to GPIO bridge. In order to connect a CAN controller device to the Qseven ® module's CAN bus it is necessary to add transceiver hardware to the carrier board.

## 6.2. eMMC (option)

The Embedded Multimedia Flash Card (eMMC) is eMMC 5.1 compatible and supports eMMC flash capacities from 2 GByte to 32 GByte (pSLC) or from 2 GByte to 64 GByte (MLC). During the manufacturing process, Multi Level Cell (MLC) eMMC is reconfigured to act as pseudo Single Level Cell (pSLC) eMMC to provide improved reliability, endurance and performance.

The eMMC flash memory features are:

- Up to 32 GByte (pSLC) / 64 GB (MLC) eMMC 5.1 Flash

- eMMC 5.1 compatible

#### 6.3. Debug Port - JTAG

The Joint Test Action Group (JTAG) is an industry standard used to verify designs and test modules or boards after they have been manufactured. JTAG tests for common problems by observing data at the device's inputs and controlling the data at the outputs. Simple tests can be performed to find manufacturing defects such as missing devices unconnected pins or failed/dead devices. The JTAG signals are: TDI (Test Data In), TDO (Test Data Out), TMS (Test Mode Select), TCK (Test Clock), and TRST (Test Report-optional).

#### 6.4. Fast I2C

Fast I2C (100 to 400 kHz) supports transfer between components on the same board. The Qseven-Q7ALx2 features two I2C Interfaces. One standard I2C interface and one I2C interface multiplexed with the SM Bus.

The I2C controller supports:

- Multimaster transfers

- Clock stretching

- Collision detection

- Interruption on completion of an operation

#### 6.5. GPIO

The eight GPIO pins GPIO0 (pin 185), GPIO1 (pin 186), GPIO2 (pin 187), GPIO3 (pin 188), GPIO4 (pin 189), GPIO5 (pin 190), GPIO6 (pin 191) and GPIO7 (pin 192) on the Qseven® connector are pin shared with the LPC. An EEPROM bit is added so that the carrier board can define if the pins are used as GPIO or LPC.

The GPIO or LPC option is configured in the BIOS setup:

Advanced>CPLD Configuration>GPIO-LPC Mux Select [Mux to LPC, Mux to GPIO]

### 6.6. Kontron Security Solution (option)

The Kontron security solution is a combined hardware and software solution that includes an embedded hardware security module and a software framework to protect applications.

The integrated security module connected to SoC port 7. Therefore, if this option is installed, SoC port 7 is not available for other interfaces. The main integrate security solution features are:

- Copy protection

- ▶ IP protection

- License model enforcement

If required, customers can customize the solution to meet specific needs. For more information, contact <u>Kontron</u> Support.

#### 6.7. LPC

The Low Pin Count (LPC) interface signals are connected to the LPC bus bridge located in the CPU or integrated chipset. The LPC low speed interface can be used for peripheral circuits such as an external Super I/O controller that typically combines legacy-device support into a single IC. The implementation of this sub-system complies with the Qseven® Specification.

The LPC bus does not support DMA (Direct Memory Access). When more than one device is used on LPC, a zero delay clock buffer is required that can lead to limitations for the ISA bus.

The LPC Interface signals LPC\_AD0 (pin 185), LPC\_AD1 (pin 186), LPC\_AD2 (pin 187), LPC\_AD3 (pin 188), LPC\_CLK (pin 189), LPC\_FRAME# (pin 190) and LPC\_LDRQ# (pin 192) on the Qseven® connector are pin shared with the GPIO. The CPLD controller incorporates a LPC bridge to support either I2C, to GPIO. An EEPROM bit on the carrier board can define if the pins are used as GPIO or LPC.

The GPIO or LPC option is configured in the BIOS setup:

Advanced>CPLD Configuration>GPIO-LPC Mux Select [Mux to LPC, Mux to GPIO]

Table 8: Supported BIOS Features

| LPC           | Interface Signals | Description                               |

|---------------|-------------------|-------------------------------------------|

| LPC Bridge to | UART              | 4-wire UART                               |

|               | GPIO              | 8x GPIOs                                  |

|               | CAN               | Used GPIO bridge to support CAN interface |

|               | I2C               | I2C interface                             |

|               | PS/2              | Not supported                             |

|               | LPT               | Not suppored                              |

|               | Floppy            | Not supported                             |

Interface signal marked as not supported (PS/2, LPT and Floppy) do not exclude OS support (e.g. Hardware Monitor (HWM) is accessible via SMB). If any other LPC Super I/O additional BIOS implementations are necessary, contact Kontron Support.

#### 6.8. RTC

The Real Time Clock (RTC) keeps track of the current time accuratly. The RTC's low power consumption means that the RTC can be powered from an alternative source of power, enabling the RTC to continue to keep time while the primary source of power is off or unavailable. The Q7ALx2 module's RTC battery voltage range is 2.4 V - 3.3 V.

#### 6.9. SDIO

The Secure Digital Input/Output (SDIO) interface is used to interchange data between devices. Using an SDIO card, data can be interchanged between portable or non-portable memory. The 4-bit SDIO transmits data on SDIO\_DAT1 (pin 148), SDIO\_DAT1 (pin 149), SDIO\_DAT3 (pin 149) and SDIO\_DAT4 (pin 150) and controls the data using pins 142, 143, 145, 146 and 147 on the Qseven® connector.

#### 6.10. SPI

The Serial Peripheral Interface Bus (SPI) bus is a synchronous four-wire serial data link standard. Devices communicate in master/slave mode, where the master device initiates the data frame. A master device can control one or multiple slave device(s) by setting the slave's (chip select) line.

The Q7ALx2 module supports one SPI interface. The SPI interface is connected to the primary SPI chip on the module and can also be used to boot from the external BIOS SPI chip on the carrier board.

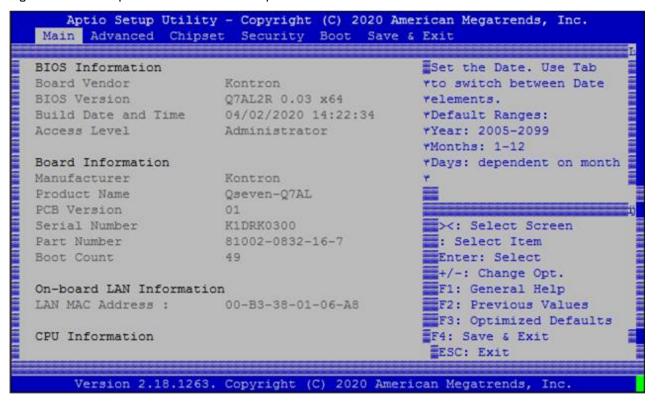

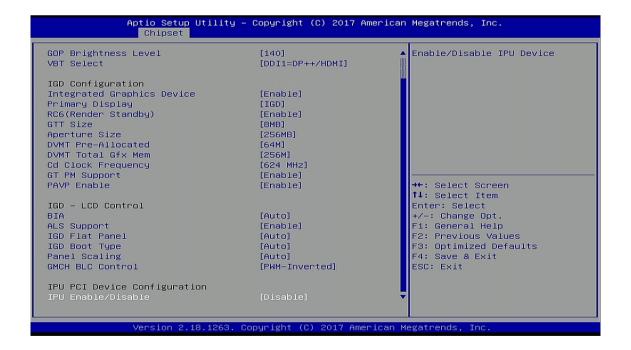

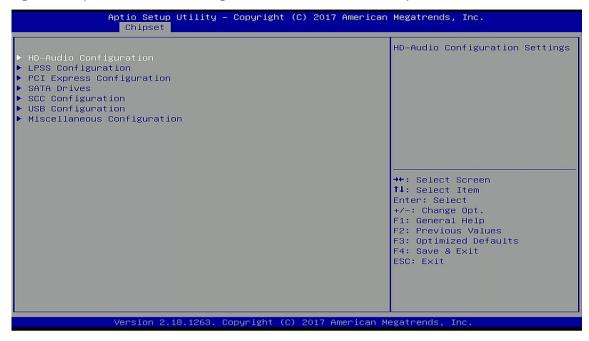

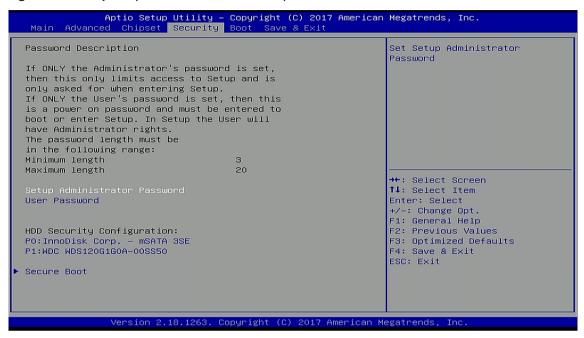

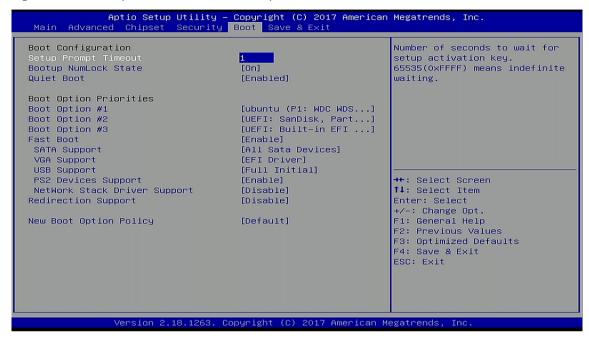

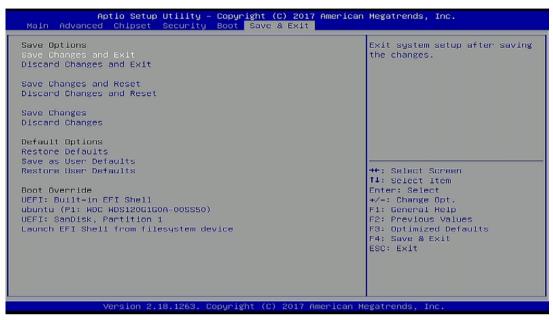

The SPI interface can boot from the primary on-module SPI chip or with an external SPI BIOS chip on the carrier board.