# **SMARC-sXAS**

User Guide Rev. 1.0

# **Table of Contents**

| 1. General Information                                          | 3        |

|-----------------------------------------------------------------|----------|

| 1.1 Disclaimer                                                  | 3        |

| 1.2 Intended Use                                                | 4        |

| 1.3 Terms and Conditions                                        | 5        |

| 1.4 Customer Support                                            | 5        |

| 1.5 Customer Service                                            | 5        |

| 1.6 Customer Comments                                           | 5        |

| 1.7 Symbols                                                     | 6        |

| 1.8 For Your Safety                                             | 7        |

| 1.9 High Voltage Safety Instructions                            | 7        |

| 1.10 Special Handling and Unpacking Instruction                 | 7        |

| 1.11 Lithium Battery Precautions                                | 8        |

| 1.12 General Instructions on Usage                              |          |

| 1.13 Quality and Environmental Management                       | 9        |

| 1.13.1 Disposal and Recycling                                   | 9        |

| 1.13.2 WEEE Compliance                                          | 9        |

| 2. Introduction                                                 | 10       |

| 2.1 Product Naming Clarification                                | 10       |

| 2.2 Description                                                 | 10       |

| 2.3 SMARC-sXAS Module                                           | 11       |

| 3. Product specification                                        | 12       |

| 3.1 Module Variants                                             | 12       |

| 3.1.1 Commercial Temperature Grade Modules (0°C to +60°C)       | 12       |

| 3.1.2 Industrial Temperature Grade Modules (E2, -40°C to +85°C) | 12       |

| 3.2 Accessories                                                 | 12       |

| 3.2.1 Cooling                                                   | 12       |

| 3.2.2 Evaluation Carrier                                        | 12       |

| 3.2.3 Mounting                                                  | 13       |

| 3.3 Functional Specification                                    | 13       |

| 3.3.1 Technical Data                                            | 13       |

| 3.3.2 Block Diagram                                             | 14       |

| 3.3.3 Top Side                                                  | 15       |

| 3.3.4 Bottom Side                                               | 16       |

| 3.3.5 Processor (CPU)                                           | 16       |

| 3.3.6 Plattform Controller Hub (PCH)                            | 18       |

| 3.3.7 System Memory                                             |          |

| 3.3.8 HSIO Mapping                                              | 18       |

| 3.4 Interfaces                                                  | 18       |

| 3.4.1 PCle                                                      | 18       |

| 3.4.2 USB                                                       | 18       |

| 3.4.3 SATA 3.0                                                  | 19       |

| 3.4.4 Graphics Interfaces                                       |          |

| 3.4.5 Audio Interface                                           |          |

| 3.4.6 UART Interfaces                                           |          |

| 3.4.7 Boot SPI Interface                                        | 21       |

|                                                                 |          |

| 3.4.8 General Purpose SPI (GSPI) / eSPI                         | 21       |

| 3.4.8 General Purpose SPI (GSPI) / eSPI                         | 21<br>22 |

| 3.4.12 SMB                                    | 23 |

|-----------------------------------------------|----|

| 3.3.13 CAN Bus                                | 23 |

| 3.4.14 Ethernet                               | 23 |

| 3.4.15 MIPI CSI                               |    |

| 3.5 Features                                  |    |

| 3.5.1 ACPI Power States                       |    |

| 3.5.2 Embedded Controller                     |    |

| 3.5.3 Trusted Platform Module                 |    |

| 3.5.4 Watchdog                                |    |

| 3.5.5 RTC                                     |    |

| 3.5.6 eMMC Flash Memory                       |    |

| 3.5.7 EEPROM                                  |    |

| 3.5.8 Features on Request                     |    |

| 3.6 Electrical Specification                  |    |

| 3.7 Thermal Management                        |    |

| 3.7.1 Heatspreader                            |    |

| 3.7.2 Thermal Sensors                         |    |

| 3.7.3 Fan Connector                           |    |

| 3.8 Mechanical Specification                  |    |

| 3.8.1 Mechanical Drawings                     |    |

| 3.9 Environmental Specification               |    |

| 3.10 Compliance                               |    |

| 3.11 MTBF                                     |    |

| 4. Pin Definitions                            |    |

| 4.1.1 Pinout of SMARC Connector (Top Side)    |    |

| 4.1.2 Pinout of SMARC Connector (Bottom Side) |    |

| 5. UEFI BIOS                                  |    |

| 5.1 Starting the UEFI BIOS                    |    |

| 5.2 Navigating the UEFI BIOS                  |    |

| 5.3 Setup Menus                               |    |

| 5.4 Getting Help                              |    |

| 5.5 UEFI Shell                                |    |

| 5.5.1 Entering the UEFI Shell                 |    |

| 5.5.2 Exiting the UEFI Shell                  |    |

| 5.6 UEFI Shell Scripting                      |    |

| 5.6.1 Startup Scripting                       |    |

| 5.6.2 Create a Startup Script                 |    |

| 5.6.3 Example of Startup Scripts              |    |

| 5.7 Firmware Update                           |    |

| 6. Technical Support                          |    |

| 6.1 Warranty                                  |    |

| 6.2 Returning Defective Material              |    |

| 7. Document Revision                          |    |

| List of Acronyms                              | 70 |

# 1. General Information

### 1.1 Disclaimer

JUMPtec would like to point out that the information contained in this user guide may be subject to alteration, particularly as a result of the constant upgrading of JUMPtec products. This document does not entail any guarantee on the part of JUMPtec with respect to technical processes described in the user guide or any product characteristics set out in the user guide. JUMPtec assumes no responsibility or liability for the use of the described product(s), conveys no license or title under any patent, copyright or mask work rights to these products and makes no representations or warranties that these products are free from patent, copyright or mask work right infringement unless otherwise specified. Applications that are described in this user guide are for illustration purposes only. JUMPtec makes no representation or warranty that such application will be suitable for the specified use without further testing or modification. JUMPtec expressly informs the user that this user guide only contains a general description of processes and instructions which may not be applicable in every individual case. In cases of doubt, please contact JUMPtec.

This user guide is protected by copyright. All rights are reserved by JUMPtec. No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means (electronic, mechanical, photocopying, recording, or otherwise), without the express written permission of JUMPtec. JUMPtec points out that the information contained in this user guide is constantly being updated in line with the technical alterations and improvements made by JUMPtec to the products and thus this user guide only reflects the technical status of the products by JUMPtec at the time of publishing.

Brand and product names are trademarks or registered trademarks of their respective owners.

©2025 by JUMPtec GmbH

JUMPtec GmbH Brunnwiesenstraße 16 94469 Deggendorf Germany www.jumptec.com

www.jumptec.com 3/71

### 1.2 Intended Use

THIS DEVICE AND ASSOCIATED SOFTWARE ARE NOT DESIGNED, MANUFACTURED OR INTENDED FOR USE OR RESALE FOR THE OPERATION OF NUCLEAR FACILITIES, THE NAVIGATION, CONTROL OR COMMUNICATION SYSTEMS FOR AIRCRAFT OR OTHER TRANSPORTATION, AIR TRAFFIC CONTROL, LIFE SUPPORT OR LIFE SUSTAINING APPLICATIONS, WEAPONS SYSTEMS, OR ANY OTHER APPLICATION IN A HAZARDOUS ENVIRONMENT, OR REQUIRING FAIL-SAFE PERFORMANCE, OR IN WHICH THE FAILURE OF PRODUCTS COULD LEAD DIRECTLY TO DEATH, PERSONAL INJURY, OR SEVERE PHYSICAL OR ENVIRONMENTAL DAMAGE (COLLECTIVELY, "HIGH RISK APPLICATIONS").

You understand and agree that your use of JUMPtec devices as a component in High Risk Applications is entirely at your risk. To minimize the risks associated with your products and applications, you should provide adequate design and operating safeguards. You are solely responsible for compliance with all legal, regulatory, safety, and security related requirements concerning your products. You are responsible to ensure that your systems (and any JUMPtec hardware or software components incorporated in your systems) meet all applicable requirements. Unless otherwise stated in the product documentation, the JUMPtec device is not provided with error-tolerance capabilities and cannot therefore be deemed as being engineered, manufactured or setup to be compliant for implementation or for resale as device in High Risk Applications. All application and safety related information in this document (including application descriptions, suggested safety measures, suggested JUMPtec products, and other materials) is provided for reference only.

Handling and operation of the product is permitted only for trained personnel within a work place that is access controlled. Follow the "General Safety Instructions" supplied with the product.

You find the most recent version of the "General Safety Instructions" online in the download area of this product on our JUMPtec website.

This product is not suited for storage or operation in corrosive environments, in particular under exposure to sulfur and chlorine and their compounds. For information on how to harden electronics and mechanics against these stress conditions, contact JUMPtec Support.

www.jumptec.com 4/71

### 1.3 Terms and Conditions

JUMPtec warrants products in accordance with defined regional warranty periods. For more information about warranty compliance and conformity, and the warranty period in your region, visit <a href="https://www.jumptec.com/en/terms-and-conditions">https://www.jumptec.com/en/terms-and-conditions</a>.

JUMPtec sells products worldwide and declares regional General Terms & Conditions of Sale, and Purchase Order Terms & Conditions. Visit <a href="https://www.jumptec.com/en/terms-and-conditions">https://www.jumptec.com/en/terms-and-conditions</a>.

For contact information, please visit our website CONTACT US.

# 1.4 Customer Support

Find JUMPtec contacts by visiting: https://www.jumptec.com/en/service-support.

### 1.5 Customer Service

As a trusted technology innovator and global solutions provider, JUMPtec extends its embedded market strengths into a services portfolio allowing companies to break the barriers of traditional product lifecycles. Proven product expertise coupled with collaborative and highly-experienced support enables JUMPtec to provide exceptional peace of mind to build and maintain successful products. For more details on JUMPtec's service offerings such as: enhanced repair services, extended warranty, training academy, and more visit <a href="https://www.jumptec.com/en/service-support">https://www.jumptec.com/en/service-support</a>.

### 1.6 Customer Comments

If you have any difficulties using this user guide, discover an error, or just want to provide some feedback, contact JUMPtec Support. Detail any errors you find. We will correct the errors or problems as soon as possible and post the revised user guide on our website.

www.jumptec.com 5/71

# 1.7 Symbols

The following symbols may be used in this user guide of SMARC-sXAS

Simple Box

Info-Box

Important-Box

Alert-Box

Tip-Box

Help-Box

Todo-Box

Download-Box

www.jumptec.com 6/71

# 1.8 For Your Safety

Your new JUMPtec product was developed and tested carefully to provide all features necessary to ensure its compliance with electrical safety requirements. It was also designed for a long fault-free life. However, the life expectancy of your product can be drastically reduced by improper treatment during unpacking and installation. Therefore, in the interest of your own safety and of the correct operation of your new JUMPtec product, you are requested to conform with the following guidelines.

# 1.9 High Voltage Safety Instructions

As a precaution and in case of danger, the power connector must be easily accessible. The power connector is the product's main disconnect device.

#### Warning

All operations on this product must be carried out by sufficiently skilled personnel only.

#### **Electric Shock!**

Before installing a non hot-swappable JUMPtec product into a system always ensure that your mains power is switched off. This also applies to the installation of piggybacks. Serious electrical shock hazards can exist during all installation, repair, and maintenance operations on this product. Therefore, always unplug the power cable and any other cables which provide external voltages before performing any work on this product. Earth ground connection to vehicle's chassis or a central grounding point shall remain connected. The earth ground cable shall be the last cable to be disconnected or the first cable to be connected when performing installation or removal procedures on this product.

# 1.10 Special Handling and Unpacking Instruction

#### **ESD Sensitive Device!**

Electronic boards and their components are sensitive to static electricity. Therefore, care must be taken during all handling operations and inspections of this product, in order to ensure product integrity at all times.

Do not handle this product out of its protective enclosure while it is not used for operational purposes

www.jumptec.com 7/71

unless it is otherwise protected.

Whenever possible, unpack or pack this product only at EOS/ESD safe work stations. Where a safe work station is not guaranteed, it is important for the user to be electrically discharged before touching the product with his/her hands or tools. This is most easily done by touching a metal part of your system housing.

It is particularly important to observe standard anti-static precautions when changing piggybacks, ROM devices, jumper settings etc. If the product contains batteries for RTC or memory backup, ensure that the product is not placed on conductive surfaces, including anti-static plastics or sponges. They can cause short circuits and damage the batteries or conductive circuits on the product.

# 1.11 Lithium Battery Precautions

If your product is equipped with a lithium battery, take the following precautions when replacing the battery.

#### Danger of explosion if the battery is replaced incorrectly.

- Replace only with same or equivalent battery type recommended by the manufacturer.

- Dispose of used batteries according to the manufacturer's instructions.

# 1.12 General Instructions on Usage

In order to maintain JUMPtec's product warranty, this product must not be altered or modified in any way. Changes or modifications to the product, that are not explicitly approved by JUMPtec and described in this user guide or received from JUMPtec Support as a special handling instruction, will void your warranty.

This product should only be installed in or connected to systems that fulfill all necessary technical and specific environmental requirements. This also applies to the operational temperature range of the specific board version that must not be exceeded. If batteries are present, their temperature restrictions must be taken into account. In performing all necessary installation and application operations, only follow the instructions supplied by the present user guide.

Keep all the original packaging material for future storage or warranty shipments. If it is necessary to store or ship the product, then re-pack it in the same manner as it was delivered. Special care is necessary when handling or unpacking the product. See Special Handling and Unpacking Instruction.

www.jumptec.com 8/71

# 1.13 Quality and Environmental Management

JUMPtec aims to deliver reliable high-end products designed and built for quality, and aims to complying with environmental laws, regulations, and other environmentally oriented requirements. For more information regarding JUMPtec's quality and environmental responsibilities, visit <a href="https://www.jumptec.com/en/about-jumptec/quality">https://www.jumptec.com/en/about-jumptec/quality</a>.

#### 1.13.1 Disposal and Recycling

JUMPtec's products are manufactured to satisfy environmental protection requirements where possible. Many of the components used are capable of being recycled. Final disposal of this product after its service life must be accomplished in accordance with applicable country, state, or local laws or regulations.

#### 1.13.2 WEEE Compliance

The Waste Electrical and Electronic Equipment (WEEE) Directive aims to:

- Reduce waste arising from electrical and electronic equipment (EEE)

- Make producers of EEE responsible for the environmental impact of their products, especially when the product become waste

- Encourage separate collection and subsequent treatment, reuse, recovery, recycling and sound environmental disposal of EEE

- Improve the environmental performance of all those involved during the lifecycle of EEE

Environmental protection is a high priority with JUMPtec.

JUMPtec follows the WEEE directive.

You are encouraged to return our products for proper disposal.

www.jumptec.com 9/71

# 2. Introduction

This user guide describes the Smart Mobility Architecture (SMARC) Computer-On-Module SMARC-sXAS made by JUMPtec and focuses on describing the module's special features. JUMPtec recommends users to study this user guide before powering on the module.

# 2.1 Product Naming Clarification

SMARC® defines a Computer-On-Module (COM), with all the components necessary for a bootable host computer, packaged as a super component. The product name for JUMPtec SMARC® Computer-On-Modules consists of:

| Standard short form | Module size | Architecture                    | _                | Available temperature variants                         |

|---------------------|-------------|---------------------------------|------------------|--------------------------------------------------------|

| SMARC-              |             | X = X86<br>$\Delta = \Delta RM$ | AL = Apollo Lake | (none=) Commercial<br>Extended (E1)<br>Industrial (E2) |

Table 1: SMARC® Product Naming Clarification

# 2.2 Description

The SMARC™ standard was developed especially for new modules with SOC processors. Modules with this interfaces are characterized by the extremely flat form factor. The SMARC or MXM 3.0 connector comes with 314 pins and a construction height of just 4.3 millimeters. The connector is also available in a shock- and vibration resistant version for rough environmental conditions. Furthermore, the standard integrates dedicated interfaces for the latest processors. OEMs profit from minimized design effort and low Bill of Material (BoM) costs. SMARC™ defines two different module sizes in order to offer a high level of flexibility regarding different mechanical requirements.

www.jumptec.com 10/71

# 2.3 SMARC-sXAS Module

The SMARC-sXAS is a SMARC half-size module using the Intel® Atom®/Pentium®/Celeron® 7xxx processor family and based on the latest SMARC 2.2 specification.

Figure 1: SMARC-sXAS

#### General features are:

- Up to 16 GByte LPDDRx memory down with in-band ECC support

- Dual LVDS, HDMI, DP++

- 1x USB 3.2

- 6x USB 2.0

- PCle Gen. 3

- eMMC onboard

- Industrial grade temperature

www.jumptec.com 11/71

# 3. Product specification

#### 3.1 Module Variants

#### 3.1.1 Commercial Temperature Grade Modules (0°C to +60°C)

Different versions containing commercial SKUs can be realized on project base. Please get in contact with GSS for further details.

### 3.1.2 Industrial Temperature Grade Modules (E2, -40°C to +85°C)

| Part No.        | SoC     | Cores  | Frequ.    | Memory                    | Flash            | Op. Temp.              |

|-----------------|---------|--------|-----------|---------------------------|------------------|------------------------|

| 51018-0432-R1-2 | x7211RE | 2 core | II ()(¬H7 | 4GB LPDDR5<br>memory down | 32GB eMMC<br>TLC | industrial temperature |

| 51018-0432-R2-2 | x7213RE | 2 core | 2.0GHz    | 4GB LPDDR5<br>memory down | 32GB eMMC<br>TLC | industrial temperature |

| 51018-0432-R2-4 | x7433RE | 4 core | 1.5GHz    | 4GB LPDDR5<br>memory down | 32GB eMMC<br>TLC | industrial temperature |

| 51018-0832-R2-8 | x7835RE | 8 core | 1.3GHz    | 8GB LPDDR5<br>memory down | 32GB eMMC<br>TLC | industrial temperature |

Table 2: Product Number for Industrial Grade Modules (-40°C to +85°C)

## 3.2 Accessories

Accessories are product specific or SMARC® specific accessories. For more information, contact your local JUMPtec Sales Representative or JUMPtec Inside Sales.

### 3.2.1 Cooling

A standard heat spreader solution can be used, which are available in a non-threaded (through hole) version.

| JUMPtec PN      | Product Name                       | Description                 |

|-----------------|------------------------------------|-----------------------------|

| 51018-0000-99-1 | HSP SMARC-sXAS                     | Heatspreader for SMARC-sXAS |

| 51099-0000-99-1 | SMARC PASSIVE UNI COOLER (W/O HSP) | SMARC Passive Uni Cooler    |

Table 3: Cooling Equipment SMARC-sXAS available from JUMPtec

#### 3.2.2 Evaluation Carrier

www.jumptec.com 12/71

| JUMPtec PN      | Product Name | Description                                                                                           |

|-----------------|--------------|-------------------------------------------------------------------------------------------------------|

| 51301-0000-00-0 |              | SMARC Evaluation Carrier for SMARC modules according to the SMARC 2.1 standard (without SMARC module) |

Table 4: Evaluation Carrier from JUMPtec

# 3.2.3 Mounting

| JUMPtec PN      | Product Name       | Description                    |

|-----------------|--------------------|--------------------------------|

| 51117-0000-00-0 | SMARC MOUNTING KIT | Mounting Kit for SMARC modules |

Table 5: Mounting Kit from JUMPtec

# 3.3 Functional Specification

### 3.3.1 Technical Data

| COMPLIANCE             | SMARC module 2.2                                                               |

|------------------------|--------------------------------------------------------------------------------|

| DIMENSIONS (H X W X D) | 82 x 50 mm                                                                     |

| CPU                    | Intel Amston Lake SKUs – Industrial RE-Series                                  |

| CHIPSET                | -                                                                              |

| MAIN MEMORY            | Up to 16 GByte LPDDR5 memory down with inband ECC support                      |

| GRAPHICS CONTROLLER    | Gen 12 IGFX                                                                    |

| ETHERNET               | Up to 2.5GbE                                                                   |

| STORAGE                | 1x SATA 6Gb/s                                                                  |

| FLASH ONBOARD          | up to 256 GByte eMMC (TLC, pSLC optional)                                      |

| PCI EXPRESS®           | up to 4x PCle x1                                                               |

| PANEL SIGNAL           | 1x HDMI (on request DP++), 1x DP++, 1x Dual LVDS (on request eDP)              |

| USB                    | 1x USB 3.2, 6x USB 2.0                                                         |

| SERIAL                 | 4x UART ( 2x RX/TX only)                                                       |

| OTHERS FEATURES        | HD Audio, I <sup>2</sup> C, 2x SPI, 14x GPIOs                                  |

| SPECIAL FEATURES       | Trusted Platform Module TPM 2.0 Industrial Temperature Grade versions          |

| FEATURES ON REQUEST    | eMMC: up to 85 GByte pSLC<br>RAM: from 2 GByte to 16 GByte LPDDR4              |

| BIOS                   | AMI UEFI                                                                       |

| OPERATING SYSTEM       | Windows® 10 (IOT) Enterprise x64, Windows® 11, Linux                           |

| POWER SUPPLY           | 5V only! No Widerange                                                          |

| TEMPERATURE            | Industrial grade:<br>-40°C to +85°C operating,<br>-40°C to +85°C non-operating |

| HUMIDITY               | 93 % relative Humidity at 40 °C, non-condensing (according to IEC 60068-2-78)  |

|                        |                                                                                |

Table 6: Technical Data

www.jumptec.com 13/71

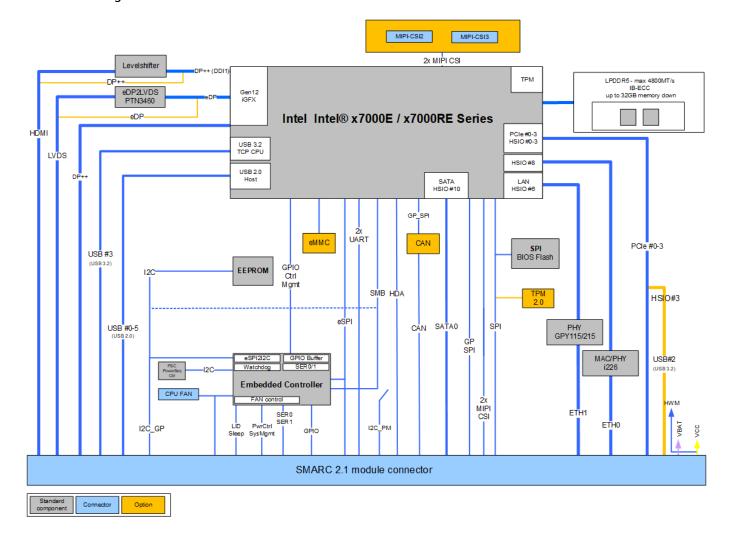

# 3.3.2 Block Diagram

The block diagram shows all availabale SMARC-sXAS interfaces.

Figure 2: SMARC-sXAS Blockdiagram

www.jumptec.com 14/71

# **3.3.3 Top Side**

Figure 3: SMARC-sXAS Front Side

- 1. Mounting Holes

- 2. SMARC Connector

- 3. Fan Connector

- 4. Optional eMMC

- 5. LPDDR5

- 6. SoC

www.jumptec.com 15/71

# 3.3.4 Bottom Side

Figure 4: SMARC-sXAS Bottom Side

- 1. Mounting Holes

- 2. SMARC Connector

### 3.3.5 Processor (CPU)

The Intel Atom®/Pentium®/Celeron® 7xxx processor family is the base for the SMARC-sXAS.

|          |           | x7211RE               | x7213RE | x7433RE | x7833RE |  |

|----------|-----------|-----------------------|---------|---------|---------|--|

| TDP      |           | 6W                    | 9W      | 9W 12W  |         |  |

| Core     | S         | 2                     |         | 4 8     |         |  |

|          | Base      | 1.0GHz                | 2.0GHz  | 1.5GHz  | 1.3GHz  |  |

| CPU      | 1C Turbo  | 3.2GHz                | 3.4GHz  | 3.4GHz  | 3.6GHz  |  |

| MC Turbo |           | 2.9GHz 2.9GHz 2.7GHz  |         | 3.0GHz  |         |  |

|          | EU        | 16                    | EU      | 32EU    |         |  |

| GPU      | Base      | 400MHz                | 600MHz  | 600MHz  | 800MHz  |  |

|          | Turbo     | 1.0GHz                | 1.0GHz  | 1.0GHz  | 1.2GHz  |  |

| ECC      |           | Yes-In Band           |         |         |         |  |

| TCC I    | RealTime  | Yes                   |         |         |         |  |

| Use (    | Condition | Embedded / Industrial |         |         |         |  |

Table 7: Atom®/Pentium®/Celeron® 7xxx processor family

When RE-Series is used as Embedded use condition DTR = +-90°C For use as Industrial use condition turbo needs to be disabled - DTR = +-110°C

www.jumptec.com 16/71

#### Intel® DTR (Dynamic Temperature Range)

For this processor family the Dynamic Temperature Range (DTR) behavior applies. DTR is the temperature range the processor can operate in. The temperature range starts with the temperature of the processor (Tj = junction temperature) at boot time and can transition to a lower and/or higher temperature within the Tj min and Tj max limits.

E.g.: Tj min = -40°, the Tj max =  $100^{\circ}$ C and the DTR = +-90°C TBoot = -40°C: the processor can operate from -40°C up to + 50°C TBoot = -20°C: the processor can operate from -40°C up to + 70°C TBoot = +20°C: the processor can operate from -40°C up to + 100°C

A Tj outside of the DTR range requires a cold reset but is not enforced by the hardware.

The behavior is described in Intel whitepaper 814861 as DTR = Dynamic Temperature Range. Please contact JUMPtec Support for further information.

| CPU Use Condition            | Industrial    | Embedded     |

|------------------------------|---------------|--------------|

| CPU Tjunction Min.           | -40ºC         | 0°C          |

| Max.                         | TBoot + 110ºC | TBoot + 70ºC |

| DTR (Hot to Cold Transition) | TBoot - 110ºC | TBoot - 70ºC |

Table 8: DTR temperatures

In Industrial use condition, the following design recommendations must be in place for the entire duration of the product's operating lifetime to meet Intel's goals.

(Activity Factor (AF) is defined as the percentage of time that the interface signals are switching while the processor is active (in an S0 state) across the entire use condition duration.)

- The VCCANA power rail must be implemented in FIVR Mode. Implementing VCCANA in MBVR (Motherboard Voltage Regulator) Mode is not allowed.

- HW is already prepared for FIVR mode

- VCCANA FIVR Mode must also be enabled using the following soft strap: CPU Straps ⇒ CPU Straps ⇒ VCCANA VR Location = VCCANA is CPU FIVR

- The CPU & GPU Intel® Turbo Boost Technology 2.0 features should be disabled by the system BIOS, so the maximum frequency is limited to the HFM value.

- For the eMMC & TCSS interfaces, two design recommendation options are listed.

Only one out of two of these options should be implemented:

- Reduced Activity Factor

- Reduced Freq

For further details please get in contact with JUMPtec Support.

www.jumptec.com 17/71

### 3.3.6 Plattform Controller Hub (PCH)

The Atom®/Pentium®/Celeron® 7xxx processor family provides an On-Package PCH.

#### 3.3.7 System Memory

The SMARC-sXAS supports up to 16 GByte LPDDR5 memory down (4800MT/s). The Intel Atom  $\times$ 7000RE and  $\times$ 7000E processor series supports in-band ECC.

#### 3.3.8 HSIO Mapping

The integrated SoC PCH supports 9x HSIO lanes, which can be configured as PCIe Gen 3.0 lanes with a max of 5 RPC (Root Port Controller). Partially the HSIOs are multi-pupose and can be alternatively configured as USB3.2 Gen2 or SATA.

| <b>HSIO Lane</b> | 0          | 1          | 2          | 3                            | 6     | 8                | 9    | 10      | 11      |

|------------------|------------|------------|------------|------------------------------|-------|------------------|------|---------|---------|

| Default          | PCle       | PCle       | PCIe       | PCIe                         | GbE 1 | PCIe             | PCIe | SATA #0 | SATA #1 |

| SMARC Connector  | PCle<br>#A | PCIe<br>#B | PCIe<br>#C | PCIe #D<br>Optional<br>USB#2 | GbE1  | GbE0 via<br>i226 | N.C. | SATA #0 | N.C.    |

Table 9: HSIO Mapping

### 3.4 Interfaces

#### 3.4.1 PCle

The SMARC-sXAS supports up to four high-speed PCI Express 3.0 lanes PCIe [0-3], allowing for the connection of up to four separate external PCIe devices. The default PCIe configuration is  $(4 \times 1)$  with options for  $(1 \times 2 + 2 \times 1)$ ,  $(2 \times 2)$  and  $(1 \times 4)$ .

| <b>SMARC Connector</b> | <b>HSIO Lane</b> | HSIO Port | Supp | orted | Lane | Config |

|------------------------|------------------|-----------|------|-------|------|--------|

| PCIE_A                 | 0                | PCIE 1 #1 | x1   | x2    | x2   | ×4     |

| PCIE_B                 | 1                | PCIE 1 #2 | x1   |       | XZ   |        |

| PCIE_C                 | 2                | PCIE 1 #3 | x1   | x1    | x2   | - x4   |

| PCIE_D                 | 4                | PCIE 1 #4 | x1   | x1    | _ XZ |        |

Table 10: PCI Express

#### 3.4.2 USB

The SMARC-sXAS provides one (optional two) USB 3.2 (10.0 Gb/S) SuperSpeed port(s) backwards compatible with USB 2.0 and six dedicated USB 2.0 ports.

www.jumptec.com 18/71

#### **USB 3.2**

| <b>SMARC Connector</b> | CPU  | Description                                   |

|------------------------|------|-----------------------------------------------|

| USB2 SS                | TCP1 | USB-C Port used as 3.2 Gen2 (10Gb/s) to SMARC |

Table 11: USB 3.2

#### **USB 2.0**

| <b>SMARC Connector</b> | <b>PCH USB Port</b> | Description                                            |

|------------------------|---------------------|--------------------------------------------------------|

| USB0                   | USB2 1              | -                                                      |

| USB1                   | USB2 2              | -                                                      |

| USB2                   | USB2 6              | TCP1 has to be paired with PCH USB2 Port 1, 2, 5 or 6. |

| USB3                   | USB2 3              | -                                                      |

| USB4                   | USB2 4              | -                                                      |

| USB5                   | USB2 5              | -                                                      |

Table 12: USB 2.0

#### **USB 2.0 Client Mode**

The USB subsystem also supports Dual Role Capability. The xHCl is paired with a standalone eXtensible Device Controller Interface (xDCl) to provide dual role functionality. The xDCl can be mapped to any of the USB ports, but there is only one endpoint supported. As SMARC-sXAS does not have an onboard Type-C PD controller, it supports static USB2.0 device mode only (No USB3.0 support due to the limitation by fixed USB\_ID in software).

It does not support changing dynamically between host mode and device mode. A BIOS settings change in setup menu and restart is required.

When designing the carrier board consider the speed of the USB 3.2 Gen2 (10 Gb/s). JUMPtec recommends using a retimer/redriver on the carrier.

#### 3.4.3 SATA 3.0

The SMARC-sXAS provides one SATA III 6Gb/s port.

| <b>SMARC Connector</b> | <b>HSIO Lane</b> | <b>HSIO Port</b> | Description         |

|------------------------|------------------|------------------|---------------------|

| SATA0                  | 10               | SATA 0           | SATA 6Gb/s to SMARC |

Table 13: SATA ports

www.jumptec.com 19/71

### 3.4.4 Graphics Interfaces

The processor graphics are based on the Generation 12 graphics core architecture. The Gen 12 architecture supports up to 32 Execution Units (EUs), depending on the processor SKU. AML processor supports three simultaneous displays (Pipes A, B, C).

| Processor | SMARC Port        |               |  |

|-----------|-------------------|---------------|--|

| DDIA      | LVDS eDP (option) |               |  |

| DDIB      | HDMI (d           | ptional DP++) |  |

| TCP0      | DP++              |               |  |

Table 14: Graphic Interfaces

#### 3.4.5 Audio Interface

HDA signals will passed through directly to SMARC.

| <b>SMARC Connector</b> | PCH Pin  | Description                      |

|------------------------|----------|----------------------------------|

| HDA_RST#               | HDA_RST# |                                  |

| HDA_SYNC               | HDA_SYNC |                                  |

| HDA_CLK                | HDA_BCLK | 24.0 MHz clock to external codec |

| HDA_SDO                | HDA_SDO  |                                  |

| HDA_SDI                | HDA_SDI0 |                                  |

Table 15: HDA

#### 3.4.6 UART Interfaces

SMARC-SXAS support four serial ports. The ports are designated SER0 – SER3. Ports SER0 and SER2 are 4 wire ports (2 data lines and 2 handshake lines). Ports SER1 and SER3 are 2 wire ports (data only).

- Two UARTs provided from Embedded Controller

- Two UARTs provided by CPU

| SMARC Signal | CPU Pin            | <b>Embedded Controller Pin</b> |

|--------------|--------------------|--------------------------------|

| SER0_TX      | -                  | GPIO104/UART0_TX               |

| SER0_RX      | -                  | GPIO105/UARTO_RX               |

| SER0_RTS#    | -                  | GPIO144/UARTO_RTS#             |

| SER0_CTS#    | -                  | GPIO143/UARTO_CTS#             |

| SER1_TX      | -                  | GPIO170/UART1_TX               |

| SER1_RX      | -                  | GPIO171/UART1_RX               |

| SER2_TX      | GPP_H11/UART0_TXD  | -                              |

| SER2_RX      | GPP_H10/UART0_RXD  | -                              |

| SER2_RTS#    | GPP_H12/UART0_RTS# | -                              |

| SER2_CTS#    | GPP_H13/UART0_CTS# | -                              |

www.jumptec.com 20/71

| <b>SMARC Signal</b> | CPU Pin           | <b>Embedded Controller Pin</b> |

|---------------------|-------------------|--------------------------------|

| SER3_TX             | GPP_D18/UART1_TXD | -                              |

| SER3_RX             | GPP_D17/UART1_RXD | -                              |

Table 16: UART Serial Ports

#### 3.4.7 Boot SPI Interface

The Serial Peripheral Interface (SPI) bus is a synchronous serial data link where devices communicate in master/slave mode and the master device initiates the data frame. Multiple slave devices are allowed with individual slave select (chip select) lines.

The SPI interface may only be used with a SPI Flash device to boot from the external BIOS on the carrier board.

The SPI Flash chip stores the BIOS to be booted. The SMARC-sXAS supports SPI boot from the 32 MByte SPI Flash chip on the board and an external 32 MByte SPI Flash chip on the carrier board.

The SPI flash chip on the carrier is required to be 32MByte (256MBit).

The module's SPI voltage is 1.8V. Booting takes place either from the on-module SPI Flash chip or the external SPI Flash chip on the carrier board.

### 3.4.8 General Purpose SPI (GSPI) / eSPI

On SMARC connector side the GSPI is shared with eSPI functionality. SXAS connects a general purpose SPI (GSPI) port that's provided by the onboard embedded controller (KSC20) to those pins by default. For options please refer the table below.

So there's only one ESPI slave (Embedded Controller / KSC20) enabled in the BIOS. If a second eSPI slave on the carrier should be enabled a BIOS as well as HW modification is necessary.

General purpose SPI is provided by the SMARC Eval Carrier eSPI connector (J47).

| SMARC Pin             | GSPI (KSC20)<br>(default) | 1 -                 | GSPI (PCH)<br>(optional 2) |

|-----------------------|---------------------------|---------------------|----------------------------|

| ESPI_CS0# / SPI1_CS0# | GPIO024 / GSPI_CS#        | ESPI_CS1# / GPP_A23 | GPP_E10 / GSPI0_CS0#       |

| ESPI_CS1# / SPI1_CS1# | GPIO022                   | -                   | -                          |

| ESPI_CK / SPI1_CK     | GPIO023 / GSPI_CLK        | ESPI_CLK / GPP_A9   | GPP_E11 / GSPI0_CLK        |

www.jumptec.com 21/71

| SMARC Pin            | GSPI (KSC20)<br>(default) |                       | GSPI (PCH)<br>(optional 2) |

|----------------------|---------------------------|-----------------------|----------------------------|

| ESPI_IO_0 / SPI1_DO  | GPIO245 / GSPI_IO0        | ESPI_IO0 / GPP_A0     | GPP_E12 / GSPI0_MISO       |

| ESPI_IO_1 / SPI1_DIN | GPI0243 / GSPI_I01        | ESPI_IO1 / GPP_A1     | GPP_E13 / GSPI0_MOSI       |

| ESPI_IO_2 / -        | -                         | ESPI_IO2 / GPP_A2     | -                          |

| ESPI_IO_3 / -        | -                         | ESPI_IO3 / GPP_A3     | -                          |

| ESPI_ALERTO# / -     | -                         | ESPI_ALERT1# / GPP_A6 | -                          |

| ESPI_ALERT1# / -     | -                         | -                     | -                          |

| ESPI_RESET / -       | -                         | ESPI_RESET# / GPP_A10 | -                          |

Table 17: GSPI / eSPI

#### 3.4.10 I2C

The SMARC-sXAS contains two I2C interfaces I2C\_GP and I2C\_PM capable and a default data rates of 100 kHz.

#### 3.4.11 GPIO

The SMARC-sXAS offers 14 GPIOs, generated by the onboard embedded controller. Configuration can to be done by the OS driver.

| <b>SMARC Signal</b> | KSC     | Alternative Use |

|---------------------|---------|-----------------|

| GPIO0               | GPIO011 | CAM0_PWR#       |

| GPIO1               | GPIO012 | CAM1_PWR#       |

| GPIO2               | GPIO013 | CAM0_RST#       |

| GPIO3               | GPIO014 | CAM1_RST#       |

| GPIO4               | GPIO015 | HDA_RST#        |

| GPIO5               | GPIO002 | PWM_OUT#        |

| GPIO6               | GPIO052 | TACHIN          |

| GPIO7               | GPIO053 | -               |

| GPIO8               | GPIO054 | -               |

| GPIO9               | GPIO064 | -               |

| GPIO10              | GPIO100 | -               |

| GPIO11              | GPIO130 | -               |

| GPIO12              | GPIO131 | -               |

| GPIO13              | GPIO222 | -               |

Table 18: General Purpose IOs

Defaults in BIOS are GPIOs except HDA\_RST#, PWM\_OUT# and TACHIN.

www.jumptec.com 22/71

#### 3.4.12 SMB

The System Management Bus (SMBus) is a simple 2-wire bus for low-speed system management communication. The (On-Package) PCH controls the SMBus. It is not used onboard on the module, but routed to the SMARC connector. The SMBus address uses the LSB (Bit 0) for the direction of the device. Bit 0 = 0 defines the write address Bit 0 = 1 defines the read address

#### 3.3.13 CAN Bus

The CAN BUS communication according to ISO 11898-1 (identical to the Bosch CAN Protocol Specification 2.0 part A, B) and according to ISO 11898-4 (Time-triggered Communication on CAN). The Can Bus controller supports communication according to CAN FD Protocol Specification 1.0. The CAN FD option can be used together with event-triggered CAN communication.

| <b>SMARC Connector</b> | SoC Pin     | Description                |

|------------------------|-------------|----------------------------|

| CANO_TX                | PSE_CAN0_TX | Can Port 0 transmit output |

| CANO_RX                | PSE_CAN0_RX | Can Port 0 Receive output  |

| CAN1_TX                | PSE_CAN1_TX | Not supported on SXAS      |

| CAN1_RX                | PSE_CAN1_RX | Not supported on SXAS      |

Table 19: CAN Bus

#### **3.4.14 Ethernet**

There are two Gigabit Ethernet options on the SMARC-sXAS. The Amston Lake includes one Gigabit Ethernet (GbE) Time-Sensitive Networking (TSN) controller that resides in PCH. The GbE-TSN controller can operate at multiple speeds (10/100/1000 & 2500 Mbps Serial Gigabit Media-Independent Interface (SGMII)) and in either full duplex or half duplex mode.

#### **External PHY**

SXAS supports the usage of Intel GPY115 (default) Phy for 1Gbps operation as well as Intel GPY215 (optional) for speeds up to 2.5Gbps. Both Phys are pin-to-pin compatible and attached to the AML SGMII interface (PSE GbE#0, HSIO lane 7). The PHY uses an external SPI flash to support field firmware update (FFU) and load customized FW images to, for example, adjust LED pin behavior. It has an onboard OTP where the default firmware is pre-programmed.

#### 1226

One Intel Foxville I226-IT Ethernet Controller is connected to PCH HSIO Port 8 (PCIe #9).

#### 3.4.15 MIPI CSI

SMARC 2.1 defines two MIPI CSI serial camera interfaces. The defined CSI0 interface supports up to two differential data lanes (CSI0\_D[0:1]+/-). CSI1 up to four differential data lanes (CSI1\_D[0:3]+/-).

Amston Lake supports MIPI CSI-2 V2.0 only (the control interface (referred as CCI) is always a

www.jumptec.com 23/71

bidirectional control interface compatible with I2C standard).

| SMARC Pin         | Amston Lake          |

|-------------------|----------------------|

| CSI0_RX[0:1]±     | CSI_C_DP/N[0:1]      |

| CSI0_CK±          | CSI_C_CLK_P/N        |

| I2C_CAM0_CK       | GPP_H7 / I2C1_SCL    |

| I2C_CAM0_DAT      | GPP_H6 / I2C1_SDA    |

| CAM0_PWR# / GPIO0 | GPP_A21              |

| CAM0_RST# / GPIO2 | GPP_R6               |

| CAM_MCK           | GPP_H20 / IMGCLKOUT0 |

Table 20: CSI0

| SMARC Pin         | Amston Lake        |

|-------------------|--------------------|

| CSI1_RX[0:3]±     | CSI_B_DP/N[0:3]    |

| CSI1_CK±          | CSI_B_CLK_P/N      |

| I2C_CAM1_CK       | GPP_B17 / I2C5_SCL |

| I2C_CAM1_DAT      | GPP_B16 / I2C5_SDA |

| CAM1_PWR# / GPIO1 | GPP_A22            |

| CAM1_RST# / GPIO3 | GPP_R7             |

Table 21: CSI1

### 3.5 Features

#### 3.5.1 ACPI Power States

ACPI enables the system to power down, save power when not required (suspend) and wake up when required (resume). ACPI controls the power states S0-S5, where S0 has the highest priority and S5 the lowest priority.

| <b>S0</b> | Working state                                |

|-----------|----------------------------------------------|

| S1        | Sleep (typically not supported anymore)      |

| S2        | Deep Sleep (typically not supported anymore) |

| <b>S3</b> | Suspend-to-RAM                               |

| <b>S4</b> | Suspend-to-disk / Hibernate                  |

| <b>S5</b> | Soft-off state                               |

Table 22: ACPI Power States Function

Not all ACPI defined power states are available.

www.jumptec.com 24/71

The SMARC-sXAS supports ACPI 6.0 and the power states S0, S3, S4, S5. To power on from state S3, S4, S5 use: Power Button, Wake On LAN

#### 3.5.2 Embedded Controller

The Embedded Controller (EC) together with the Power Sequence Controller (PSC) provides a broad set of functionality:

- power sequencing control

- monitoring the module's processor temperature, power supply voltages V\_IN\_VAR, VCC\_5V\_SBY,

VCC\_RTC

- monitoring and configuring the on-board and external fans

- acting as hub or super-IO for low speed interfaces such as UART, I2C/SMB, GP SPI, GPIO

- supporting watchdog functions

The EC is accessible through the API in the Board Support Package.

#### 3.5.3 Trusted Platform Module

The SMARC-sXAS supports the firmware TPM (fTPM) using the integrated TPM 2.0 capability of the Intel Platform Trusted Technology (Intel® PTT). On request a dicrete TPM chip can be offered which is directly connected to the dedicated SPI interface from the PCH.

#### 3.5.4 Watchdog

The SMARC-sXAS supports an independently programmable dual-stage software watchdog timer. The watchdog functionality is accessible through the API of the Embedded Controller (EC) in the related Board Support Package. The watchdog is able to generate IRQ (SWI), SMI and SCI dependent on the implementation.

Please find more information about the watchdog implementation in the according API user guide for the EC implementation.

| Time-out event | Description                                                                                                                                                                                                                                                                   |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| No action      | Stage is off and will be skipped                                                                                                                                                                                                                                              |  |

| Reset          | Restarts the module and starts a new POST and operating system                                                                                                                                                                                                                |  |

| NMI            | A non-maskable interrupt (NMI) is a computer processor interrupt that cannot be ignored by standard interrupt masking techniques in the system. It is used typically to signal attention for non-recoverable hardware errors.                                                 |  |

| SMI            | A system management interrupt (SMI) makes the processor entering the system management mode (SMM). As such, specific BIOS code handles the interrupt. The current BIOS handler for the watchdog SMI currently does nothing. For special requirements, contact JUMPtec Support |  |

| SCI            | A system control interrupt (SCI) is a OS-visible interrupt to be handled by the OS using AML code                                                                                                                                                                             |  |

www.jumptec.com 25/71

| Time-out event | Description                                                                                                            |

|----------------|------------------------------------------------------------------------------------------------------------------------|

| ΠΙΔΙΑΝ         | Might be necessary when an operating system must be started and the time for the first trigger pulse must be extended. |

Table 23: Watchdog Events

#### 3.5.5 RTC

The RTC keeps track of the current time accurately. The RTC's low power consumption means that the RTC can be powered from an alternative source of power enabling the RTC to continue to keep time while the primary source of power is off or unavailable. The RTC's battery voltage range is 2.0 V to 3.25 V. Typical RTC values are 3 V and less than 10  $\mu$ A. If the module is powered by mains supply, the RTC voltage is generated by on-module regulators, to reduce RTC current draw. The SMARC-sXAS supports an internal RTC by default with the option for an external RTC on request such as a lithium cell or super cap on the carrier board.

Using the SMARC-sXAS without RTC battery voltage supply may result in improper behavior. Contact JUMPtec Support in case you plan a carrier design without RTC battery.

### 3.5.6 eMMC Flash Memory

The Embedded Multimedia Flash Card (eMMC) is eMMC 5.1 compatible. The standard eMMC Flash memory is TLC. On request eMMC pSLC can be offered. During the manufacturing process, Triple Level Cell (TLC) eMMC is reconfigured to act as pseudo Single Level Cell (pSLC) eMMC to provide improved reliability, endurance and performance. The module's eMMC flash memory supports up to 85 GByte pSLC or 256 GByte TLC.

Pseudo SLC (pSLC) memory is a reconfigured MLC/TLC eMMC.

$\ensuremath{\mathsf{MLC}}$  to pSLC: the capacity is half of a MLC memory.

TLC to pSLC: the capacity is a third of the TLC memory.

#### **3.5.7 EEPROM**

The embedded EEPROM (EeeP) is connected to I2C\_GP bus from the CPLD and operates at 1.8 V. The EEEP address is A0h (8bit format). The EEPROM retains module parameter information, including the module serial number and data structure and conforms to the PICMG® EEEP Embedded EEPROM Specification.

www.jumptec.com 26/71

#### 3.5.8 Features on Request

For the SMARC-sXAS following optional features are available on request:

| Optional Features (on request) |                                                                                               |  |

|--------------------------------|-----------------------------------------------------------------------------------------------|--|

| Feature                        | Description                                                                                   |  |

| x7000E                         | CPU from x7000E processor series                                                              |  |

| LPDDR5                         | Memory down up to 16 GB                                                                       |  |

| eMMC 5.1                       | Up to 256GB eMMC 5.1 Flash<br>TLC technology - configuration as pSLC can be offered           |  |

| TPM                            | Discrete TPM 2.0 chip                                                                         |  |

| eDP                            | Support of eDP instead of LVDS                                                                |  |

| eSPI                           | Instead of LPC signals, eSPI signals are routed to the according pins of the SMARC connector  |  |

| UART                           | 2 UART serial RX/TX ports from SOC (PCIe based, non-legacy) instead of Embedded<br>Controller |  |

| GP-SPI                         | Signals routed to SPI pins of SMARC connector                                                 |  |

| MIPI-CSI                       | Connecting flatfoil                                                                           |  |

| USB 3.2                        | 2nd USB 3.2 instead of PCIe#3                                                                 |  |

Table 24: Features on Request

# 3.6 Electrical Specification

The SMARC-sXAS powers on by connecting to a carrier board via the SMARC connector. Before connecting the module to the carrier board, ensure that the carrier board is switch off and disconnected from the main power supply at the time of connection. Failure to disconnect the main power supply from the carrier board could result in personal injury and damage to the module and/or carrier board. The SMARC connector pins on the module limits the amount of power received. The module receives power on the ten VDD-IN pins that operate over the VDD-IN range of 4.75 VDC to 5.25 VDC. The current rating of each connector pin is 0.5 A and for ten pins 5 A ( $0.5 \text{ A} \times 10$ ).

The SMARC-sXAS powers on by connecting to the carrier board using the Interface connector. Before connecting the module to the carrier board's corresponding connector, ensure that the carrier board is switch off and disconnected from the main power supply. Failure to disconnect the main power supply could result in personal injury and damage to the module and/or carrier board.

Observe that only trained personnel aware of the associated dangers connect the module, within an access controlled ESD-safe workplace.

Supply Voltage (VDD-IN) 5V only! No Widerange

www.jumptec.com 27/71

| RTC           | 2.3 VDC to 3.25 VDC                                  |  |

|---------------|------------------------------------------------------|--|

| Input Current | 5 A max. on all ten VDD_IN pins (0.5 A max. per pin) |  |

Table 25: Power Supply Voltage Requirements

Only connect to an external power supply delivering the specified input rating and complying with the requirements of Safety Extra Low Voltage (SELV) and Limited Power Source (LPS) of UL/IEC 60950-1 or (PS2) of UL/IEC 62368-1.

To protect external power lines of peripheral devices, make sure that the wires have the right diameter to withstand the maximum available current and the enclosure of the peripheral device fulfils the fire-protection requirements of IEC/EN 62368-1.

If an under voltage (brownout) condition occurs the used power supply must remain in the "off state" long enough to allow internal voltages to discharge sufficiently. Failure to observe this "off state" may mean that parts of the product or peripherals work incorrectly or suffer a reduction of MTBF. The minimum "off state", to allow internal voltages to discharge sufficiently, is dependent on the power supply and additional electrical factors. To determine the required "off state", each case must be considered individually. For more information, contact JUMPtec Support.

# 3.7 Thermal Management

### 3.7.1 Heatspreader

A heatspreader plate assembly is available from JUMPtec for the SMARC-sXAS. The heatspreader plate on top of this assembly is NOT a heat sink. It works as a SMARC-standard thermal interface to use with a heat sink or external cooling devices. External cooling must be provided to maintain the heatspreader plate at proper operating temperatures. Under worst case conditions, the cooling mechanism must maintain an ambient air and heatspreader plate temperature on any spot of the heatspreader's surface according to the module specification:

- 60°C for commercial grade modules

- 85°C for industrial temperature grade modules (E2/XT)

Documentation and CAD drawing of the heatspreader and cooling solutions are available on request from JUMPtec's Customer Section.

www.jumptec.com 28/71

JUMPtec recommends the use of thermal interfaces between the heatspreader plate and the major heat-generating components. About 80 % of the power dissipated within the module is conducted to the heatspreader plate and can be removed by the cooling solution. Heatspreaders are available as an accessory for both commercial and industrial temperature grades.

#### 3.7.2 Thermal Sensors

The SMARC-sXAS uses an on-chip thermal sensors located within the CPU to measure the CPU temperature, and a thermal sensor close to the Hardware monitor chip to measure the module temperature.

#### 3.7.3 Fan Connector

The analog output voltage on this connector is generated via a discrete linear voltage regulator from the PWM signal of the HWM. It is clipped at 12 V (+/- 10 %) across the whole input range of the module to prevent FAN damage at higher voltages. FAN signals are connected to a 3-pin-connector. The maximum supply current to the fan is 350 mA for an input voltage of 5.0 V.

| <b>Connector Pin</b> | Description  |

|----------------------|--------------|

| 1                    | FAN_TACH_IN# |

| 2                    | V_FAN        |

| 3                    | GND          |

Table 26: Fan Connector

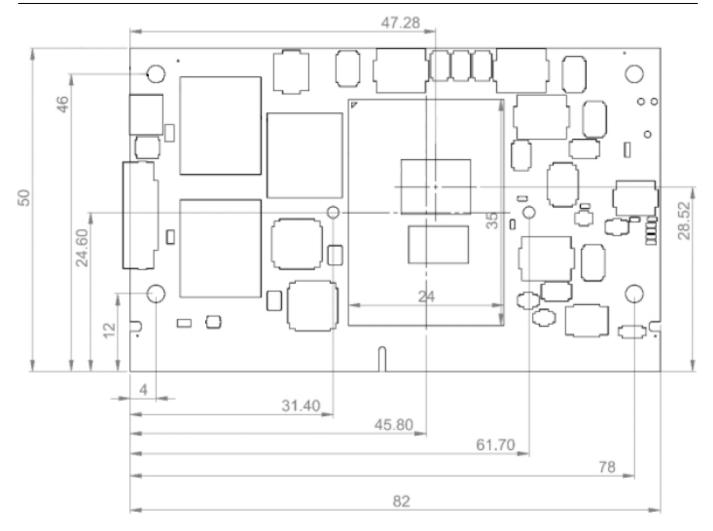

# 3.8 Mechanical Specification

The SMARC short module form factor is 82 mm x 50 mm and includes four mounting holes per SMARC specification. There are two additional holes to enable the attachment of a thermal device such as a heatsink/heatspreader. The total height of the SMARC-sXAS module depends on the height of the implemented cooling solution.

### 3.8.1 Mechanical Drawings

www.jumptec.com 29/71

# 3.9 Environmental Specification

The standard versions of the SMARC-sXAS supports industrial temperature grade only.

| Environmental                          |               | Description                                                                |

|----------------------------------------|---------------|----------------------------------------------------------------------------|

| In deserting Consults (F2)             | Operating     | -40°C to +85°C (-40°F to 185°F)                                            |

| industrial Grade (E2)                  | Non-operating | -40°C to +85°C (-40°F to 185°F) -40°C to +85°C (-40°F to 185°F)            |

| Relative Humidity                      |               | 93 % @40°C, non-condensing                                                 |

| Shock (according to IEC 60068-2-27)    |               | Non-operating shock test (half-sinusoidal, 11ms, 15g)                      |

| Vibration (according to IEC 60068-2-6) |               | Non-operating vibration (sinusoidal, 10 Hz to 2000 Hz, $\pm$ 0.15 mm, 2 g) |

Table 27: Environmental Specification

# 3.10 Compliance

The SMARC-sXAS complies with the following or the latest status thereof. If modified, the prerequisites for specific approvals may no longer apply. For more information, contact JUMPtec Support.

www.jumptec.com 30/71

|            | Europe - CE Mark                                                                                                                                                                                                                      |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Directives | 2014/30/EU: Electromagnetic Compatibility 2014/35/EU: Low Voltage 2011/65/EU: RoHS II 2001/95/EC: General Product Safety                                                                                                              |

| ЕМС        | EN 55032 Class B: Electromagnetic compatibility of multimedia equipment - Emission Requirements Class A EN 61000-6-2: Electromagnetic compatibility (EMC) Part 6-2: Generic standards - Immunity standard for industrial environments |

| Safety     | <b>EN 62368-1</b> : Audio/video, information and communication technology equipment - Part 1: Safety requirements                                                                                                                     |

Table 28: Compliance CE Mark

|        | USA/Canada                                                                                                                                                                                                                                                                                                                                              |  |  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Safety | UL 62368-1 & CSA C22.2 No. 62368-1 (Component Recognition): Audio/video, information and communication technology equipment - Part 1: Safety requirements Recognized by Underwriters Laboratories Inc. Representative samples of this component have been evaluated by UL and meet applicable UL requirements. UL listings: AZOT2.E547070 AZOT8.E547070 |  |  |

|        | UK CA Mark                                                                                                                                                                                                                                                                                                                                              |  |  |

| ЕМС    | BS EN 55032 Class B: Electromagnetic compatibility of multimedia equipment - Emission Requirements Class A BS EN 61000-6-2: Electromagnetic compatibility (EMC) Part 6-2: Generic standards - Immunity standard for industrial environments                                                                                                             |  |  |

| Safety | <b>BS EN 62368-1</b> : Audio/video, information and communication technology equipment - Part 1: Safety requirements                                                                                                                                                                                                                                    |  |  |

|        | CB scheme ( For International Certifications)                                                                                                                                                                                                                                                                                                           |  |  |

| Safety | <b>IEC 62368-1</b> : Audio/video, information and communication technology equipment - Part 1: Safety requirements                                                                                                                                                                                                                                      |  |  |

Table 29: Country Compliance

www.jumptec.com 31/71

If the product is modified, the prerequisites for specific approvals may no longer apply.

JUMPtec is not responsible for any radio television interference caused by unauthorized modifications of the delivered product or the substitution or attachment of connecting cables and equipment other than those specified by JUMPtec. The correction of interference caused by unauthorized modification, substitution or attachment is the user's responsibility.

### 3.11 MTBF

The MTBF (Mean Time Before Failure) values were calculated using a combination of the manufacturer's test data (if available) and the Telcordia (Bellcore) issue 2 calculation for the remaining parts.

The Telcordia calculation used is "Method 1 Case 3" in a ground benign, controlled environment. This particular method takes into account varying temperature and stress data and the system is assumed to have not been burned-in. Other environmental stresses (such as extreme altitude, vibration, saltwater exposure) lower MTBF values.

|              | MTBF Value @40°C | Part Number       |

|--------------|------------------|-------------------|

| MTBF (hours) | 879.034          | 51018-3285R2-9EVL |

Table 30: MTBF

The MTBF estimated value above assumes no fan, but a passive heat sinking arrangement. Estimated RTC battery life (as opposed to battery failures) is not accounted for and needs to be considered separately. Battery life depends on both temperature and operating conditions. When the module is connected to external power, the only battery drain is from leakage paths.

www.jumptec.com 32/71

# 4. Pin Definitions

The following sections provide pin definitions and detailed description of all on-board connectors. The connector definitions follow the following notation.

|             | Description                                                                         |                                                                                                                                              |  |  |

|-------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin         |                                                                                     | Shows the pin-numbers in the connector. The graphical layout of the connector definition tables is made similar to the physical connectors.  |  |  |

| Signal      |                                                                                     | The mnemonic name of the signal at the current pin. The notation "XX#" states that the signal "XX" is active low.                            |  |  |

|             | Al                                                                                  | Analog Input                                                                                                                                 |  |  |

|             | AO                                                                                  | Analog Output                                                                                                                                |  |  |

|             | I                                                                                   | Input, TTL compatible if nothing else stated                                                                                                 |  |  |

|             | Ю                                                                                   | Input / Output, TTL compatible if nothing else stated                                                                                        |  |  |

|             | IOT                                                                                 | Bi-directional tristate IO pin.                                                                                                              |  |  |

|             | IS                                                                                  | Schmitt-trigger input, TTL compatible.                                                                                                       |  |  |

| Type        | IOC                                                                                 | Input / open-collector Output, TTL compatible                                                                                                |  |  |

| Туре        | IOD                                                                                 | Input / Output, CMOS level Schmitt-triggered (Open drain output)                                                                             |  |  |

|             | NC                                                                                  | Not Connected                                                                                                                                |  |  |

|             | 0                                                                                   | Output, TTL compatible                                                                                                                       |  |  |

|             | OC                                                                                  | Output, open-collector or open-drain, TTL compatible                                                                                         |  |  |

|             | ОТ                                                                                  | Output with tri-state capability, TTL compatible                                                                                             |  |  |

|             | LVDS                                                                                | Low Voltage Differential Signal                                                                                                              |  |  |

|             | PWR                                                                                 | Power supply or ground reference pins                                                                                                        |  |  |

|             | Ioh                                                                                 | Typical current in mA flowing out of an output pin through a grounded load, while the output voltage is > 2.4 V DC (if nothing else stated). |  |  |

|             | Iol                                                                                 | Typical current in mA flowing into an output pin from a VCC connected load, while the output voltage is < 0.4 V DC (if nothing else stated)  |  |  |

| Pull U/D    | On-board pull-up or pull-down resistors on input pins or open-collector output pins |                                                                                                                                              |  |  |

| Note        | Special remarks concerning the signal                                               |                                                                                                                                              |  |  |

| Designation | n Type                                                                              | and number of item described                                                                                                                 |  |  |

Table 31: Connector Definitions

# **4.1.1 Pinout of SMARC Connector (Top Side)**

| Pin | Primary (Top)<br>Side | Description                                    | Туре         | I/O<br>Domain        | Module<br>Termination | Comment |

|-----|-----------------------|------------------------------------------------|--------------|----------------------|-----------------------|---------|

| P1  | SMB_ALERT#            | SMBus Alert#<br>(Interrupt) Signal             | I OD<br>CMOS | 1.8 to 5V<br>Standby |                       | _       |

| P2  | GND                   | Power Ground                                   | PWR<br>GND   | _                    | _                     | _       |

| Р3  | CSI1_CK+              | CSI1 differential clock input (point to point) | I D-PHY      | Runtime              | _                     | _       |

www.jumptec.com 33/71

| Pin | Primary (Top)<br>Side | Description                                                                                       | Туре                        | I/O<br>Domain   | Module<br>Termination | Comment                                                                                               |

|-----|-----------------------|---------------------------------------------------------------------------------------------------|-----------------------------|-----------------|-----------------------|-------------------------------------------------------------------------------------------------------|

| P4  | CSI1_CK-              | CSI1 differential clock input (point to point)                                                    | I D-PHY                     | Runtime         | _                     | _                                                                                                     |

| P5  | GBE1_SDP              | IEEE 1588 Trigger<br>Signal for Hardware<br>Implementation of PTP<br>(Precision Time<br>Protocol) | I/O<br>CMOS                 | 3.3V<br>Standby | PD 10K                | GPY115 GPC2 pin<br>connected by<br>default<br>optional<br>connection to PCH<br>TIME_SYNC0<br>possible |

| P6  | GBE0_SDP              | IEEE 1588 Trigger<br>Signal for Hardware<br>Implementation of PTP<br>(Precision Time<br>Protocol) | I/O<br>CMOS                 | 3.3V<br>Standby | PD 10K                | I226 SDP0 pin<br>connected by<br>default<br>optional<br>connection to PCH<br>TIME_SYNC0<br>possible   |

| P7  | CSI1_RX0+             | CSI1 differential input (point to point)                                                          | I D-PHY<br>/<br>I M-<br>PHY | Runtime         | _                     | _                                                                                                     |

| P8  | CSI1_RX0-             | CSI1 differential input (point to point)                                                          | I D-PHY<br>/<br>I M-<br>PHY | Runtime         | _                     | _                                                                                                     |

| Р9  | GND                   | Power Ground                                                                                      | PWR<br>GND                  | _               | _                     | _                                                                                                     |

| P10 | CSI1_RX1+             | CSI1 differential input (point to point)                                                          | I D-PHY<br>/<br>I M-<br>PHY | Runtime         | _                     | _                                                                                                     |

| P11 | CSI1_RX1-             | CSI1 differential input (point to point)                                                          | I D-PHY<br>/<br>I M-<br>PHY | Runtime         | _                     | _                                                                                                     |

| P12 | GND                   | Power Ground                                                                                      | PWR<br>GND                  | _               | _                     | _                                                                                                     |

| P13 | CSI1_RX2+             | CSI1 differential input (point to point)                                                          | I D-PHY<br>/<br>I M-<br>PHY | Runtime         | _                     | _                                                                                                     |

| P14 | CSI1_RX2-             | CSI1 differential input (point to point)                                                          | I D-PHY<br>/<br>I M-<br>PHY | Runtime         | _                     | _                                                                                                     |